# SYNTHESIS AND SIMULATION OF NOVEL MULTI VALUED LOGIC PROCESSOR ARCHITECTURE

A Thesis submitted in partial fulfillment of requirement for the award of the degree of

#### DOCTOR OF PHILOSOPHY

In

ELECTRONICS AND TELECOMMUNICATION ENGINEERING

By

## SATISH SUDHAKAR NARKHEDE

[Ref. No. PGS/1194]

Under guidance of

Dr. Bharat S. Chaudhari

Guide Dr. Gajanan K. Kharate

Co-Guide

Department of Electronics and Telecommunication Engineering Matoshri College of Engineering and Research Centre, Nasik

**FEBRUARY 2016**

## **CERTIFICATE**

This is to certify that the thesis entitled "SYNTHESIS AND SIMULATION OF NOVEL MULTI VALUED **LOGICPROCESSOR ARCHITECTURE**", being submitted by Sudhakar Narkhede partial Satish in fulfillment of requirement for the award of degree of **Doctor of Philosophy** in Electronics and Telecommunication Engineering at Savitribai Phule Pune University at Matoshri College of Engineering and Research Centre, Nasik is a bonafide record of the work carried out by him under my supervision and guidance. The results embodied in this thesis have not been submitted elsewhere in part or full for the award of any degree or diploma.

**Prof. D. D. Dighe** Head, Dept of E&TC, Matoshri College of Engineering and Research Center, Nasik **Dr. Gajanan K. Kharate** Co-Guide and Principal, Matoshri College of Engineering and Research

Center, Nasik

Dr. Bharat S. Chaudhari Guide Professor, Dept of E&TC, Maharashtra Institute of Technology, Pune

## **CERTIFICATE OF THE GUIDE**

It is certified that the work incorporated in the thesis, entitled "SYNTHESIS AND SIMULATION OF NOVEL MULTI VALUED LOGIC PROCESSOR ARCHITECTURE", being submitted by Satish Sudhakar Narkhede was carried out by the candidate under our supervision and guidance. Such material as has been obtained from other sources has been duly acknowledged in the thesis.

Dr. Gajanan K. Kharate Co-Guide Principal, Matoshri College of Engineering and Research Center, Nasik Dr. Bharat S. Chaudhari Guide Professor, Dept of E&TC, Maharashtra Institute of Technology, Pune

Date :

Place :

## **DECLARATION BY THE CANDIDATE**

I declare that the thesis entitled "SYNTHESIS AND SIMULATION OF NOVEL MULTI VALUED LOGIC PROCESSOR ARCHITECTURE", submitted by me for the degree of **Doctor of Philosophy** is the record of work carried out by me during the period from February 2009 to February 2016 under the guidance of Dr. Bharat S. Chaudhari and Dr. Gajanan K. Kharate and has not formed the basis for the award of any degree, diploma, associate ship, fellowship, titles in any other University or other Institution of Higher learning. I further declare that the material obtained by other sources has been duly acknowledged and credited in this thesis.

Date: Place: Mr. Satish Sudhakar Narkhede Research Scholar Matoshri College of Engineering and Research Center, Nasik

#### **ACKNOWLEDGEMENT**

I wish to express my first and foremost gratitude to my PhD guide Dr. Bharat S. Chaudhari and Dr. Gajanan K. Kharate without whom this study was inconceivable. I am indeed thankful to them for their valuable guidance and immense encouragement in carrying out this research.

I am thankful to Prof. D. D. Dighe, HoD, Dept. of E&TC, MCOE, Nasik, Dr. S. D. Pable Phd Coordinator, MCOE, Nasik for their support in this journey and to Dr. S.T. Gande, Principal, SITRC, Nasik for his comments and suggestions.

I sincerely appreciate valuable support and encouragement from Mr. R. S. Kothavale, Managing Trustee PICT, Pune, Mr. Swastik Sirsikar secretary PICT, Pune, Dr. P.T. Kulkarni, Principal, PICT, Pune and Dr. Yerram Ravinder, Head, Dept. of E&TC, PICT, Pune.

I am also thankful to Dr. M. V. Munot, Prof. L. P. Patil, Prof. S. S. Dudam, Dept of E&TC, PICT for their support and kind assistance in the execution of this project. I would also like to extend special thanks to my departmental and institutional colleagues at PICT.

I am greatly indebted to my parents, Late Mr. Sudhakar Narkhede and Late Mrs. Mandakini Narkhede for always be-showering their blessings and best wishes which has driven me so far and has been key to my success; today and always. I owe many thanks to my wife Dr. Kirti and son Tanay, who walked beside me, supported me along the way constantly, and encouraged me. I thank them for their patience, understanding, and love. They have been the lenders of their rights to my time.

I would like to extend my heartfelt thanks to one and all, who have helped me in this research and its successful completion.

Satish Sudhakar Narkhede

## **TABLE OF CONTENTS**

| ABSTRACT        | ix   |

|-----------------|------|

| LIST OF FIGURES | xi   |

| LIST OF TABLES  | xv   |

| ABBREVIATION    | xvii |

| 1. |     |       | INTRODUCTION                               |      |

|----|-----|-------|--------------------------------------------|------|

|    | 1.1 |       | Preamble                                   | 1.1  |

|    | 1.2 |       | Multi Valued Logic                         | 1.1  |

|    | 1.3 |       | Current Status                             | 1.4  |

|    | 1.4 |       | Motivation                                 | 1.5  |

|    | 1.5 |       | Objectives and Scope of the Research Work  | 1.6  |

|    | 1.6 |       | Organization of the Thesis                 | 1.7  |

| 2. |     |       | LITERATURE SURVEY                          |      |

|    | 2.1 |       | Ternary logic                              | 2.2  |

|    |     | 2.1.1 | Ternary Logic Preliminaries                | 2.2  |

|    |     | 2.1.2 | Ternary Algebra And Minimization           | 2.3  |

|    |     |       | Techniques                                 |      |

|    |     | 2.1.3 | Ternary Logic Gates                        | 2.6  |

|    |     | 2.1.4 | Switching Devices For The Realization Of   | 2.10 |

|    |     |       | Ternary Logic                              |      |

|    | 2.2 |       | Multi Input Floating Gate Mosfet (MIFG)    | 2.10 |

|    |     | 2.2.1 | MIFG As A Switching Device For Realization | 2.11 |

|    |     |       | Of Ternary Circuits                        |      |

|    |     | 2.2.2 | Structure Of MIFG                          | 2.12 |

|    |     | 2.2.3 | IV Characteristics of MIFG                 | 2.15 |

|    |     | 2.2.4 | Concept of Variable Switching Voltage in   | 2.17 |

|    |     |       | MIFG                                       |      |

2.3Review of digital ternary logic systems2.182.4A Brief Review of MIFGMOS transistor2.282.5Challenges and limitations of existing2.30

systems

3

## SWITCHING DEVICES FOR THE REALIZATION OF VARIOUS TERNARY CIRCUITS

| 3.1 |       | MOSFET based approach                       | 3.2  |

|-----|-------|---------------------------------------------|------|

|     | 3.1.1 | Research methodology                        | 3.2  |

|     | 3.1.2 | Simulation results and perfromance analysis | 3.3  |

|     | 3.1.3 | Discussion on MOSFET based approach         | 3.6  |

| 3.2 |       | MIFG based design of binary gates           | 3.7  |

|     | 3.2.1 | Binary inverter using MIFG-MOSFET           | 3.8  |

|     | 3.2.2 | Binary NAND using MIFG-MOSFET               | 3.9  |

|     | 3.2.3 | Binary nor using MIFG-MOSFET                | 3.10 |

|     | 3.2.4 | Discussion on MIFG based approach           | 3.11 |

| 3.3 |       | MIFG based design of ternary gates          | 3.12 |

|     | 3.3.1 | Research methodology                        | 3.12 |

|     | 3.3.2 | Simulation results                          | 3.15 |

|     | 3.3.3 | Discussion on MIFG based approach           | 3.26 |

| 3.4 |       | Ternary decoder                             | 3.27 |

|     | 3.4.1 | Research methodology and simulation         | 3.29 |

|     |       | results                                     |      |

|     | 3.4.2 | Discussion on MIFG based approach           | 3.29 |

| 3.5 |       | Design of novel ternary level shifter       | 3.30 |

|     | 3.5.1 | Research methodology and simulation         | 3.31 |

|     |       | results                                     |      |

|     | 3.5.2 | Discussion on MIFG based approach           | 3.33 |

| 3.6 |       | MIFG based design of ternary arithmetic     | 3.34 |

and logical unit

4

|     | 3.6.1 | Ternary Half Adder[THA]                   | 3.36 |

|-----|-------|-------------------------------------------|------|

|     | 3.6.2 | Ternary Full Adder [TFA]                  | 3.38 |

|     | 3.6.3 | Ternary Multiplier [TM]                   | 3.42 |

|     | 3.6.4 | Ternary Half Subtractor [THS]             | 3.43 |

|     | 3.6.5 | Ternary Full Subtractor [TFS]             | 3.45 |

|     | 3.6.6 | Ternary Comparator [TC]                   | 3.47 |

|     | 3.6.7 | Three-to-one ternary multiplexer          | 3.49 |

|     | 3.6.8 | Discussion on MIFG based TALU             | 3.49 |

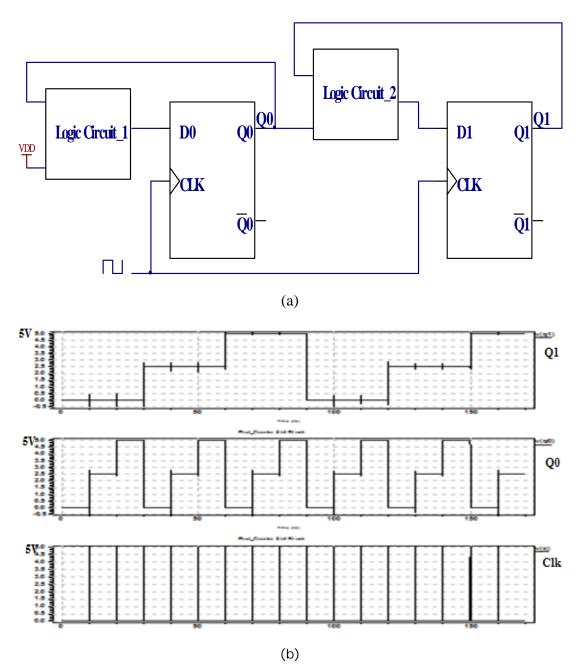

| 3.7 |       | MIFG based design of ternary sequential   | 3.50 |

|     |       | circuits                                  |      |

|     | 3.7.1 | D latch                                   | 3.50 |

|     | 3.7.2 | Ternary counter                           | 3.52 |

|     | 3.7.3 | Discussion on MIFG based ternary          | 3.57 |

|     |       | sequential circuits                       |      |

| 3.8 |       | In a nutshell                             | 3.57 |

|     |       |                                           |      |

|     |       | TESTING AND SIMULATION OF THE             |      |

|     |       | EXTENDED TERNARY LOGIC MODULES            |      |

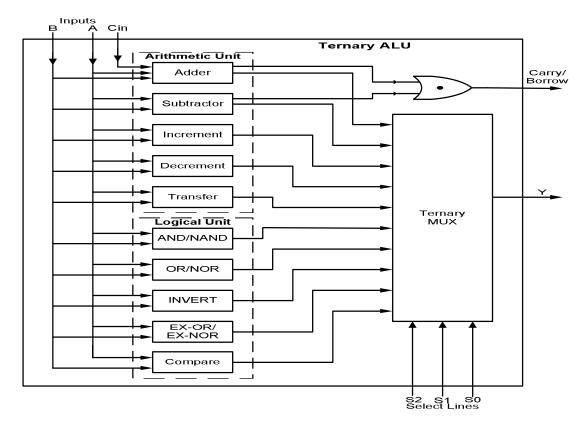

| 4.1 |       | Ternary ALU [TALU]                        | 4.1  |

|     | 4.1.1 | Research Methodology for designing TALU   | 4.2  |

|     | 4.1.2 | Simulation Results                        | 4.9  |

|     | 4.1.3 | Discussion                                | 4.13 |

| 4.2 |       | Design And Implementation of an Efficient | 4.13 |

|     |       | Ternary Control Unit (TCU)                |      |

|     | 4.2.1 | Research Methodology to Design TCU        | 4.14 |

|     | 1 2 2 | Simulation Bosults                        | 1 20 |

4.2.2

Simulation Results

4.29

4.2.3

Discussion

4.33

4.3

In the nutshell

4.34

#### 5. **RESULT ANALYSIS**

- 5.1 Analysis of the MIFG based realization of 5.1 Binary circuits

- 5.2 Analysis Of MIFG Based Ternary Gates 5.2

- 5.2.1 Performance analysis of the MIFG based 5.8 TALU

- 5.2.2 Analysis Of MIFG Based Ternary Sequential 5.14 Circuit

- 5.3 The simulation and synthesis results of 5.14 various ternary circuits

- 5.4 Major Contributions of this Research 5.17

- 5.4.1 Switching Devices for the realization Of 5.18 Various Ternary Circuits

- 5.4.2 Simulation And Testing of the Fundamentals 5.20 Units of a Ternary Processor

#### 6 CONCLUSION AND FUTURE SCOPE

6.1Conclusion6.16.2Future Directions6.3

| <b>RESEARCH PUBLICATIONS</b> | xviii |

|------------------------------|-------|

| REFERENCES                   | хх    |

#### **ABSTRACT**

Multi Valued Logic (MVL) is emerging as a thrust area of research due to several advantages offered by them over the conventional binary logic. The switching algebra has expanded from binary to penta level, progressing through ternary and quaternary levels and MVL has thereby experienced major evolution in the recent past. Ternary Logic, a logic with radix 3 i.e. 3 logic states, is a case of MVL and serves a promising alternative to the binary logic thus attracting a wide community of researchers to contribute in the design of ternary processor.Despite the potential advantages of ternary logic, realization of an efficient, realistic and a practical ternary processor is still a thrust area of research. This research aims to address some of these challenges and unidentified issues in the design of ternary processor.

With the recent technological advancements and the reported drawbacks of the CMOS level implementation, commercial realization of ternary circuits is watched with keen interest thereby motivating the wide community of researchers to explore the usability of various alternativesbeyond CMOS devices for implementing ternary circuits. This research presents a novel hybrid approach based on combination of MIFGMOS (Multi Input Floating Gate Metal Oxide Semiconductor) transistor and conventional MOSFET for the realization of the ternary gates. The basic and universal ternary gates are devised based on hybrid combination of devices. An extensive simulation of all the designed gates is carried out using TSPICE circuit simulator. The results demonstrate expected functionality of the devised hybrid gates and additionally signify improvement in the performance parameters. This research also extends the designed ternary gates to implement ternary combinational and

ix

sequential circuits and finally realize the Ternary Arithmetic and Logic Unit. An extensive simulation of the TALU is carried out for 9 operations using TSPICE circuit simulator which demonstrates expected functionality additionally signify good improvement in the and performance parameters. A modified design of ternary decoder is designed that leads to reduction in circuit element count. A novel Ternary Level Shifter which has received meager attention in the reported literature is also implemented. The design of TLS exploits the controllability and tunability of the MIFGMOS transistor to obtain an intermediate voltage level and eliminates the need of passive components and an additional power supply. This research also identifies a functionality issue in the reported design of Ternary Full Adder and proposes a solution to the identified problem. The MIFGMOS transistor based hybrid approach for designing an efficient TALU, combines the virtues of both the devices and facilitates the significant reduction in the circuit element count of the ternary combinational circuits as compared to earlier reported methods.

The arithmetic and logical unit and the control unit are essentially the most important and the nerve centre of a processor. This research presents design and implementation of an efficient 4-trit Ternary ALU and Ternary Control Unit (TCU) for a ternary processor. The implementation of sub-program overloading feature makes its design unique, flexible and portable for further extension. The functionality of the TCU is verified using fifty seven instructions belonging to various addressing modes. The control signals required for the execution of the instructions are identified and further modelled using a hardware description language.

The efficient ternary circuits designed and implemented in this research address some of the major challenges and achieve improvement in the parameters. The designed TALU and TCU signify encouraging results that pave the path for further developments in ternary processors.

Х

## List of Figures

| 2.1 | Ternary map for 2 and 3 variable                                                                                                                                                                                                                        | 2.5  |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 2.2 | Example of ternary map for 3 variable                                                                                                                                                                                                                   | 2.6  |

| 2.3 | Symbols for Inverters (a) STI (b) PTI (c) NTI                                                                                                                                                                                                           | 2.7  |

| 2.4 | Symbols for TOR/TNOR logic gates                                                                                                                                                                                                                        | 2.8  |

| 2.5 | Symbols for TAND/ TNAND logic gates                                                                                                                                                                                                                     | 2.9  |

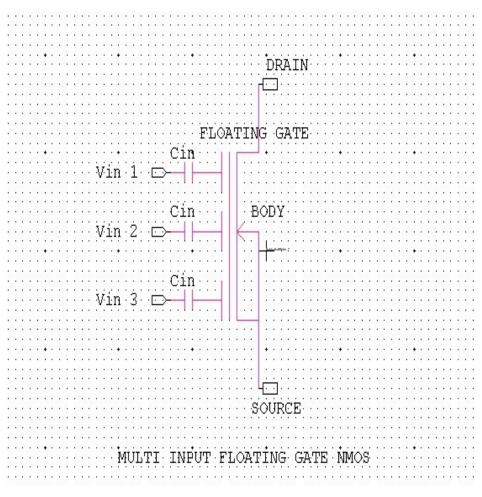

| 2.6 | MIFG MOSFET Symbol                                                                                                                                                                                                                                      | 2.12 |

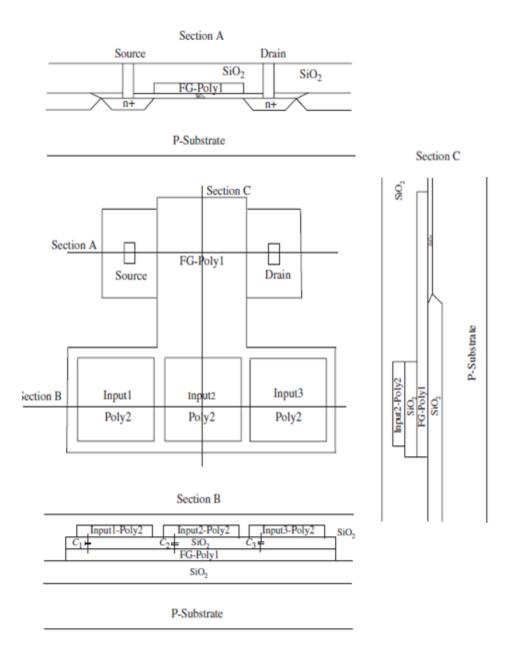

| 2.7 | Possible Layout Of a 3-input n-channel FGMOS transistor (middle) and its cross-sectional views (A, B and C)                                                                                                                                             | 2.13 |

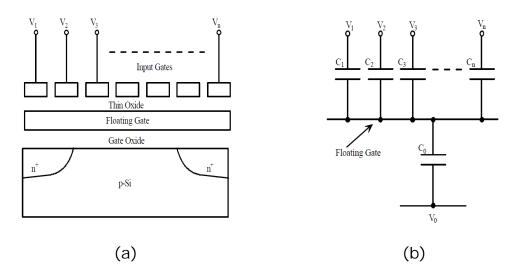

| 2.8 | Simplified structure of MIFGMOS transistor                                                                                                                                                                                                              | 2.14 |

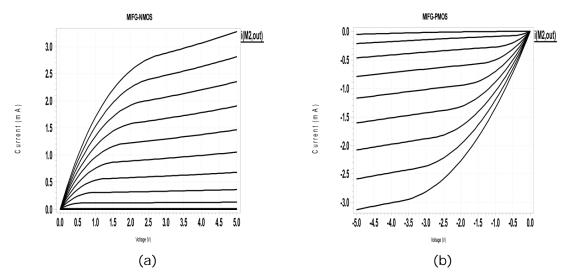

| 2.9 | IV characteristics of (a) nMIFGMOS transistor (b) MIFGMOS transistor                                                                                                                                                                                    | 2.16 |

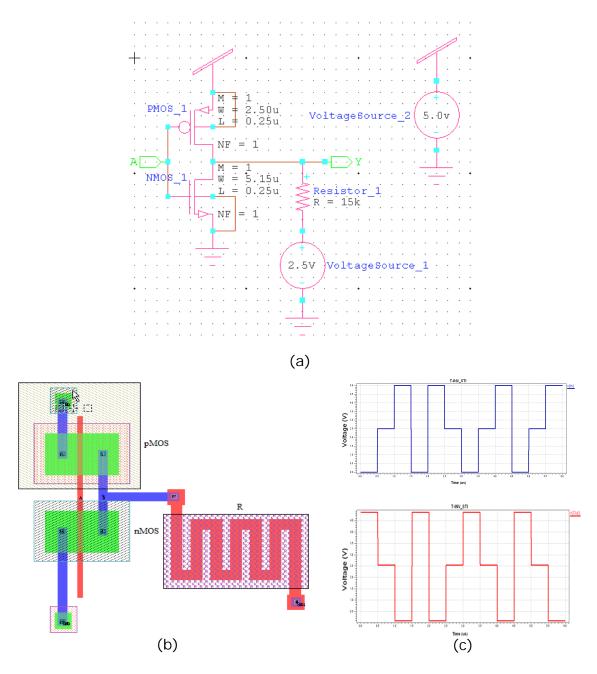

| 3.1 | Results of TNOT gate (STI gate) (a) schematic (b) layout<br>(c) simulation results                                                                                                                                                                      | 3.4  |

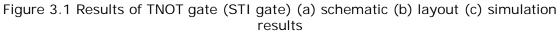

| 3.2 | Results of TNAND gate (a) schematic (b) layout (c) simulation results                                                                                                                                                                                   | 3.5  |

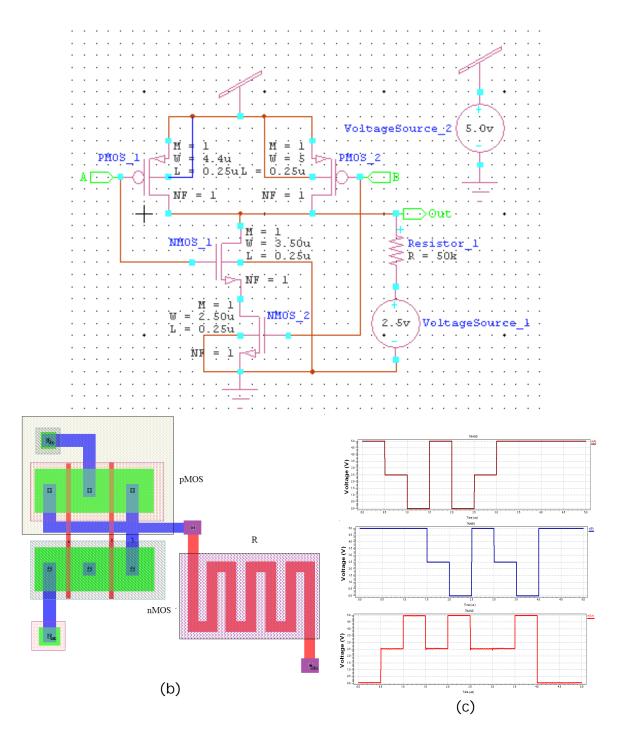

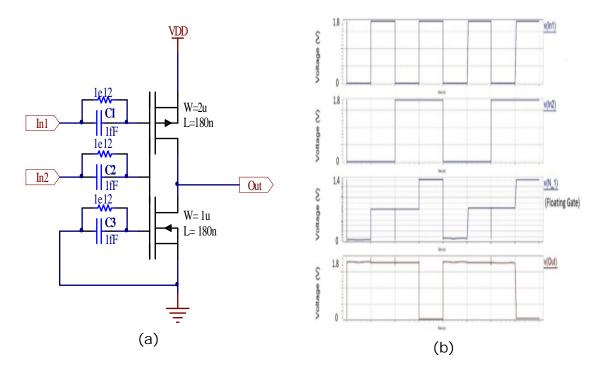

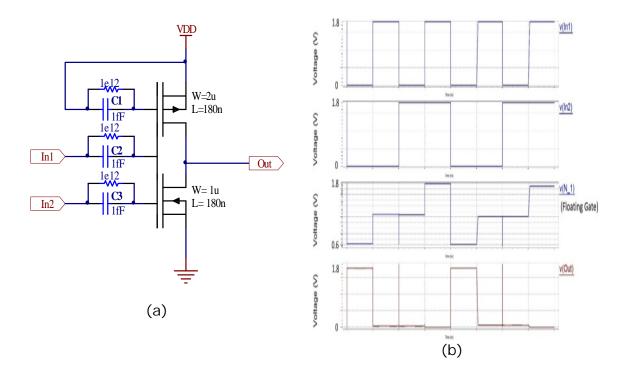

| 3.3 | (a) MIFG-MOSFET Based Inverter (b) Inverter Input Output<br>waveform                                                                                                                                                                                    | 3.9  |

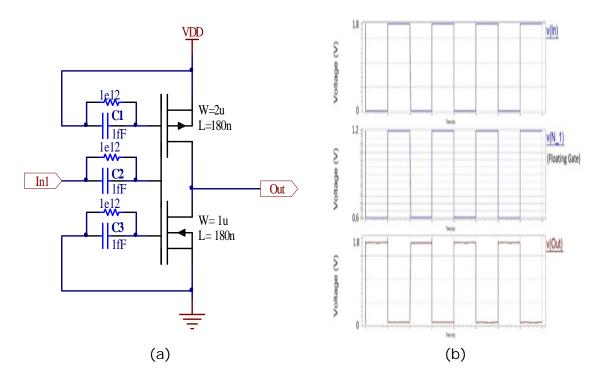

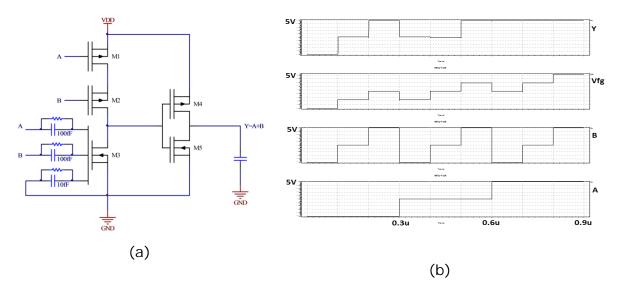

| 3.4 | (a) MIFG-MOSFET Based NAND Gate (b) NAND Gate input and output Waveforms                                                                                                                                                                                | 3.10 |

| 3.5 | (a) MIFG-MOSFET Based NOR Gate (180nm) (b)NOR Gate input and output Waveforms                                                                                                                                                                           | 3.11 |

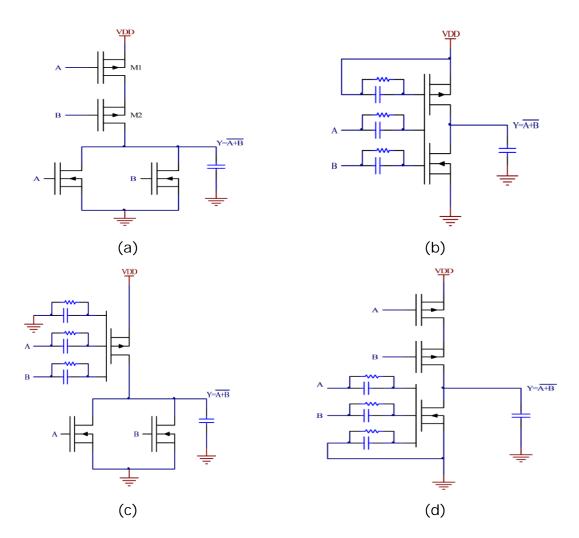

| 3.6 | (a) Conventional NOR (b) All MOSFETs are replaced by<br>MIFGMOS transistor (c) The series combination of<br>pMOSFETs is replaced by single pMIFGMOS transistor (d)<br>The parallel combination of nMOSFETs is replaced by single<br>nMIFGMOS transistor | 3.14 |

| 3.7  | (a) MIFGMOS transistor based STI (b) input and output waveform of STI                                                                                                                                  | 3.17 |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

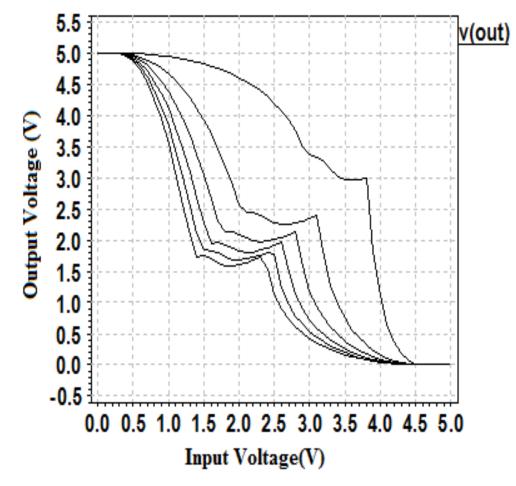

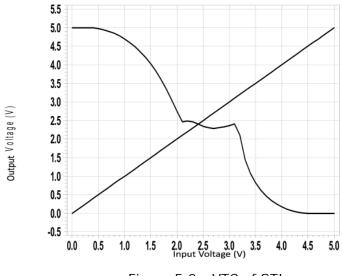

| 3.8  | VTC curve of STI                                                                                                                                                                                       | 3.18 |

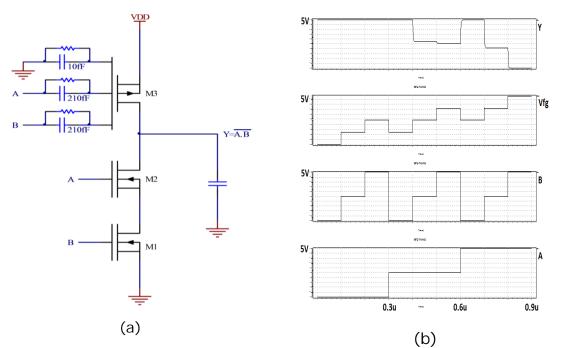

| 3.9  | (a) Ternary NAND (b) input and output waveform of T-<br>NAND                                                                                                                                           | 3.19 |

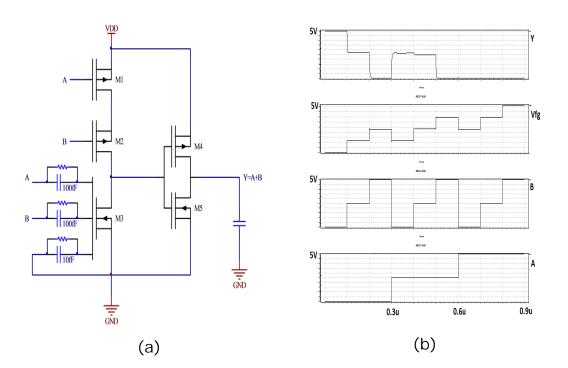

| 3.10 | (a) TNOR (b) input and output waveform of T-NOR                                                                                                                                                        | 3.22 |

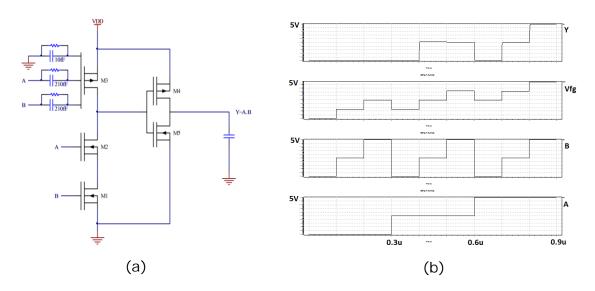

| 3.11 | (a) Ternary AND (b) input and output waveform of TOR                                                                                                                                                   | 3.25 |

| 3.12 | (a) Ternary OR (b) input and output waveform of TOR                                                                                                                                                    | 3.25 |

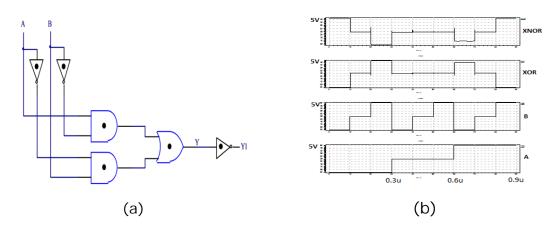

| 3.13 | (a) Ternary EXOR and EXNOR (b) input and output waveform of TEXOR and TEXNOR                                                                                                                           | 3.26 |

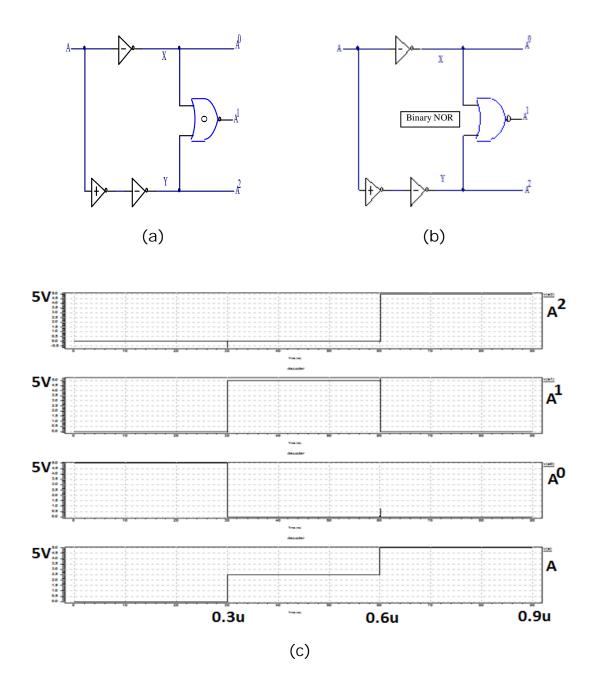

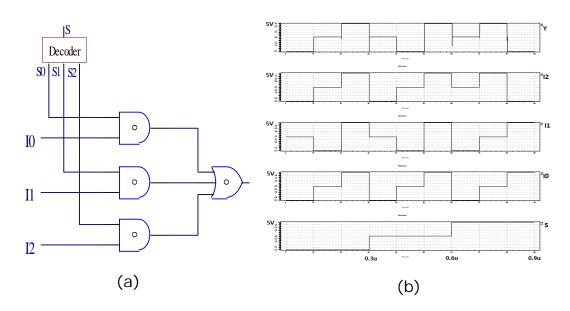

| 3.14 | (a) Conventional ternary decoder using ternary TNOR gate<br>using STI and PTI (b) Modified ternary decoder using binary<br>NOR gate (c) The input-output waveforms of the modified<br>ternary decoder. | 3.28 |

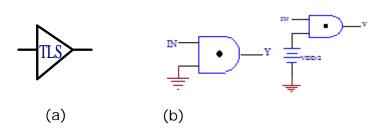

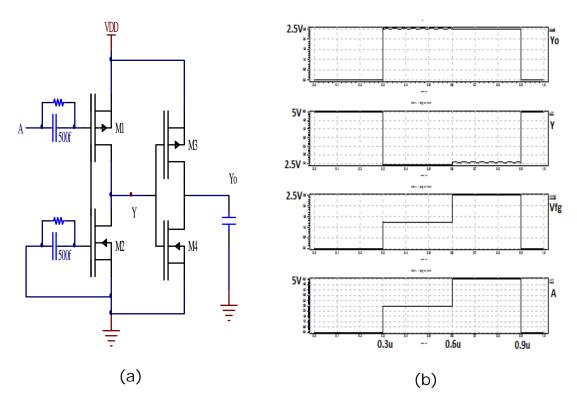

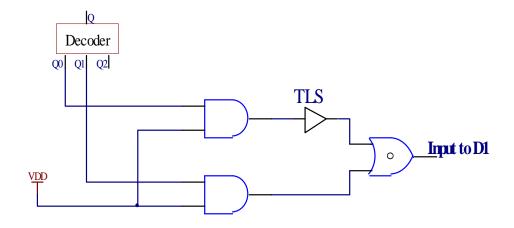

| 3.15 | (a) Symbol of TLS (b) Reported gate work as TLS                                                                                                                                                        | 3.31 |

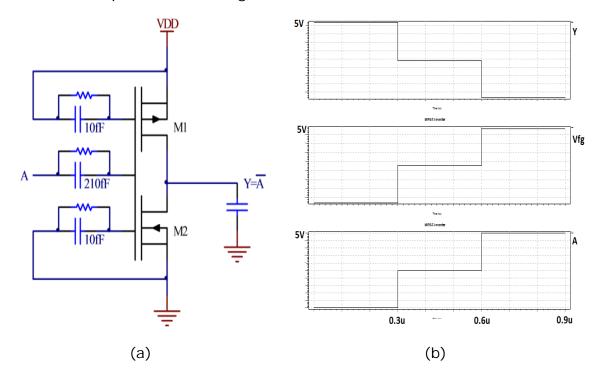

| 3.16 | (a) The proposed novel TLS (b) The input-output waveforms<br>TLS                                                                                                                                       | 3.33 |

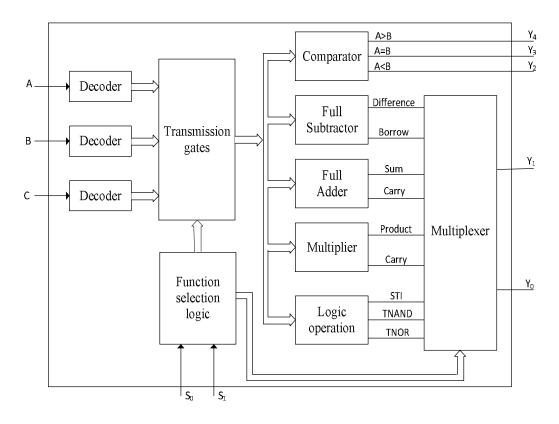

| 3.17 | Proposed MIFGMOS transistor based 1- trit TALU                                                                                                                                                         | 3.35 |

| 3.18 | Kaurnaugh Map of Ternary Half Adder                                                                                                                                                                    | 3.36 |

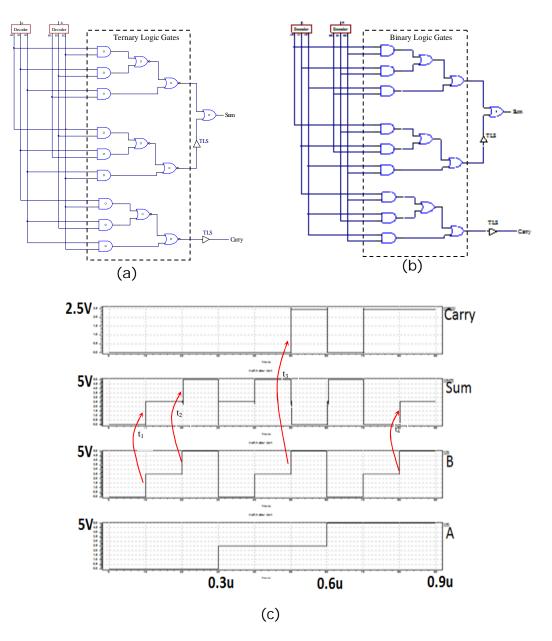

| 3.19 | (a) Logic diagram of the THA using ternary gates (b) Logic diagram of the THA using binary gates (c) The input output waveforms of the THA using binary                                                | 3.38 |

| 3.20 | <ul><li>(a) Logic block diagram of the TFA as reported in [2013_6]</li><li>(b) Proposed modified logic design of the TFA (c) The input output waveforms of the modified TFA</li></ul>                  | 3.40 |

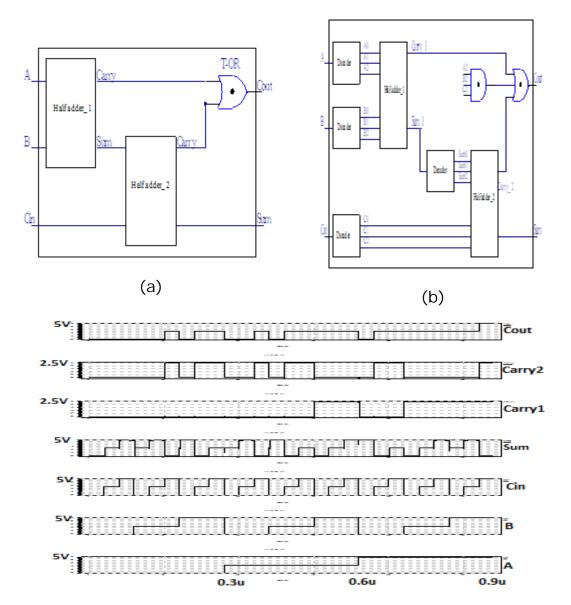

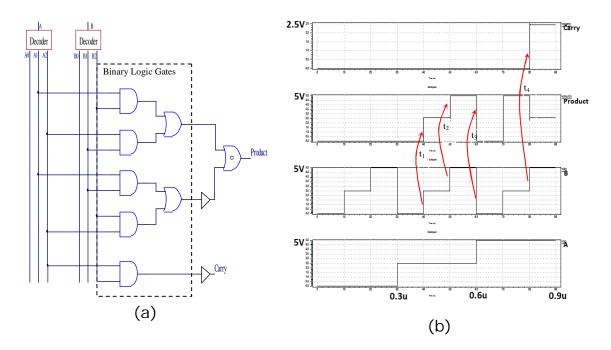

| 3.21 | (a) MIFGMOS transistor based ternary multiplier using binary gates (b) The input-output waveforms of the ternary multiplier                                                                            | 3.43 |

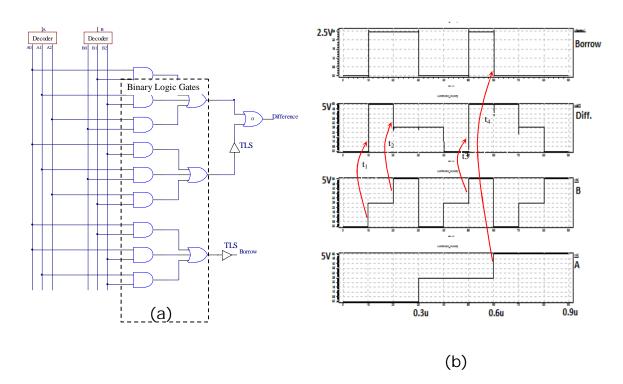

| 3.22 | (a) MIFGMOS transistor based THS using binary gates (b)<br>The input-output waveforms of the THS                                                                                                       | 3.45 |

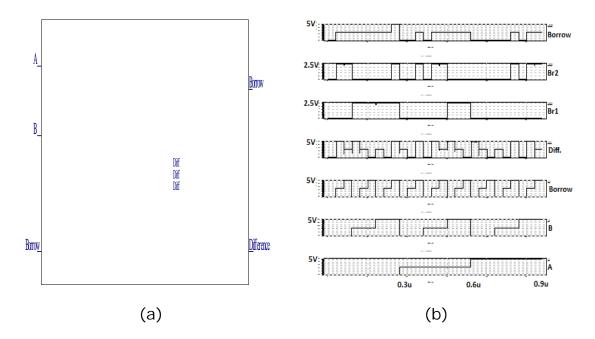

| 3.23 | (a) Proposed logic design of TFS (b) Input output waveforms of the TFS                                                                                                                                 | 3.47 |

xii

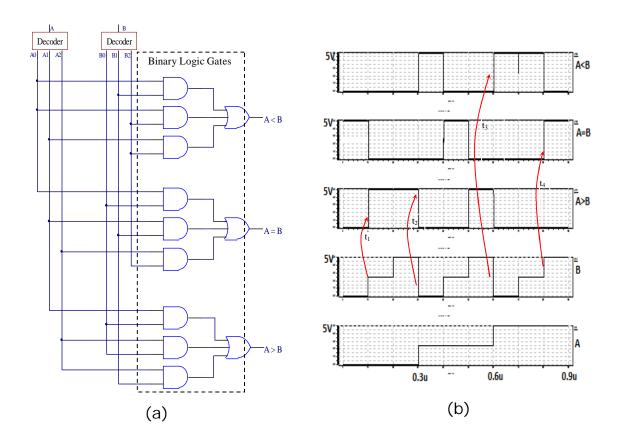

| 3.24  | (a) MIFGMOS transistor based TC using binary gates (b)                   | 3.48 |

|-------|--------------------------------------------------------------------------|------|

|       | The input-output waveforms of the TC                                     |      |

| 3.25  | (a) MIFGMOS transistor based ternary multiplexer using                   | 3.49 |

|       | binary gates (b) The input-output waveforms of the ternary               |      |

|       | multiplexer.                                                             |      |

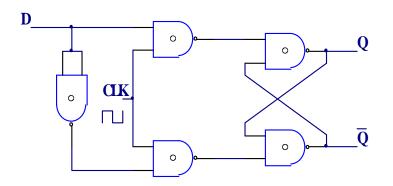

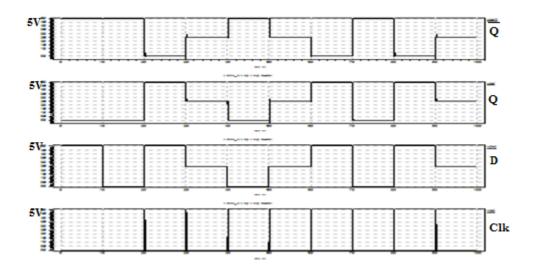

| 3.26  | D flip-flap-flop                                                         | 3.51 |

| 3.27  | Input and output waveform of D flip-flap-flop                            | 3.51 |

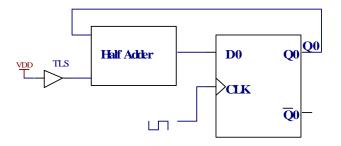

| 3.28  | 1 trit counter                                                           | 3.54 |

| 3.29  | Modified combinational circuit for 1 trit counter                        | 3.55 |

| 3.30  | (a) 2 trit counter (b) Input and Output waveform of 2 <sup>nd</sup> trit | 3.56 |

|       | counter                                                                  |      |

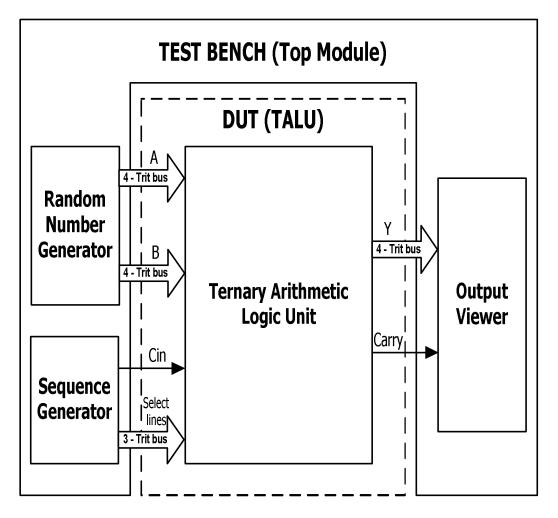

| 4.1   | Block schematic of the proposed TALU                                     | 4.3  |

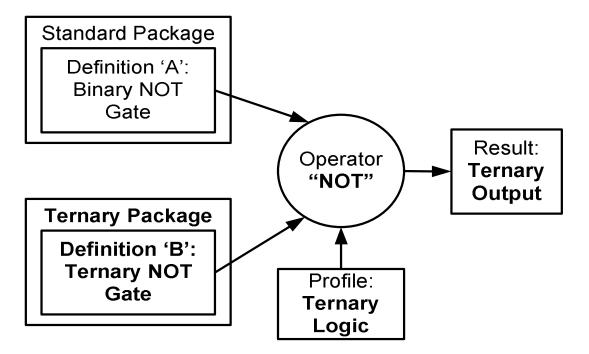

| 4.2   | Concept of sub-program overloading                                       | 4.8  |

| 4.3   | Testing and verification of the proposed TALU                            | 4.9  |

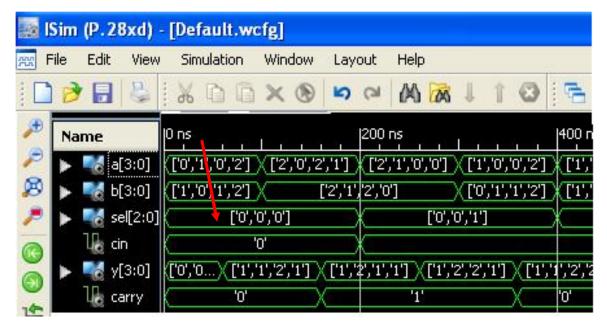

| 4.4   | Simulation results of various arithmetic operations without              | 4.10 |

|       | considering the delay component                                          |      |

| 4.5   | Simulation results of various logical operations without                 | 4.10 |

|       | considering the delay component                                          |      |

| 4.6   | Simulation results of various arithmetic operations with                 | 4.12 |

|       | considering the delay component                                          |      |

| 4.7   | Simulation results of various logical operations considering             | 4.12 |

|       | the delay component                                                      |      |

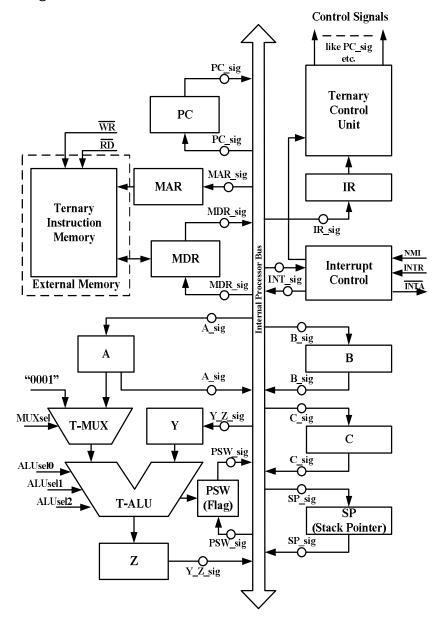

| 4.8   | Data flow diagram of the ternary processor                               | 4.14 |

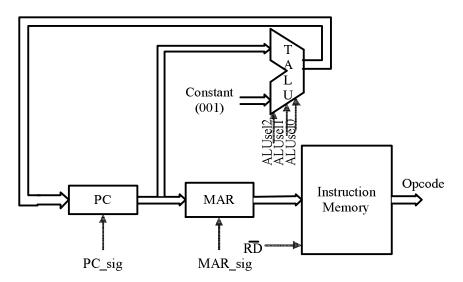

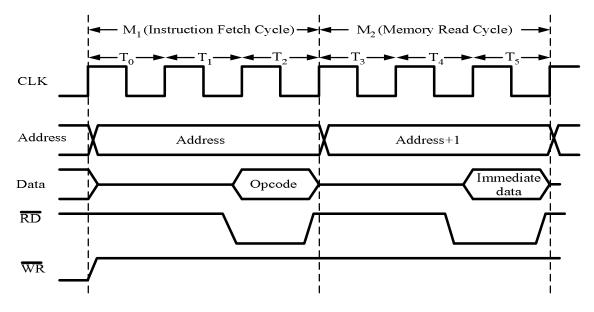

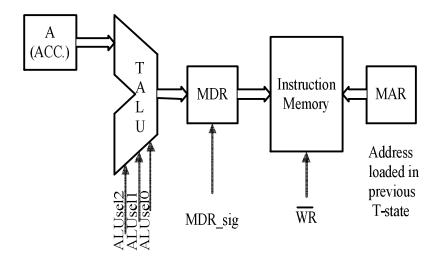

| 4.9   | Data path for instruction fetch                                          | 4.20 |

| 4.10  | Timing diagram for instruction T_MVI A, #data                            | 4.22 |

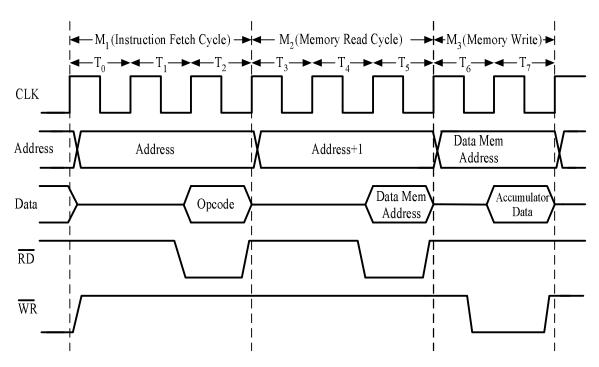

| 4.11  | Data path for memory write operation                                     | 4.23 |

| 4.12  | Timing diagram for instruction T_STA addr                                | 4.24 |

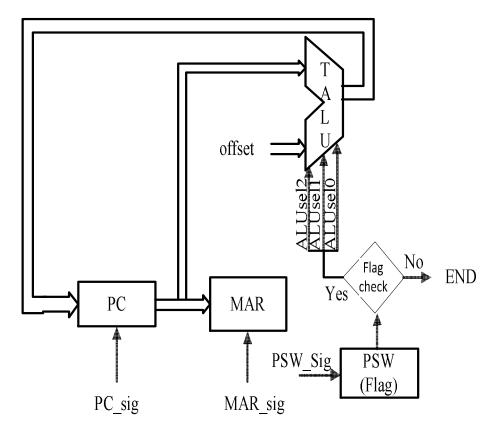

| 4.13  | Data path for conditional branch instruction                             | 4.25 |

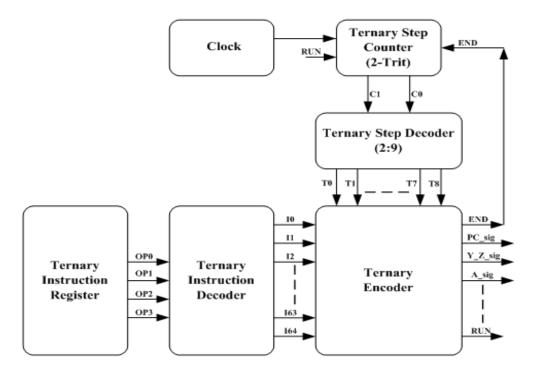

| 4.14  | The fundamental blocks in the proposed TCU                               | 4.29 |

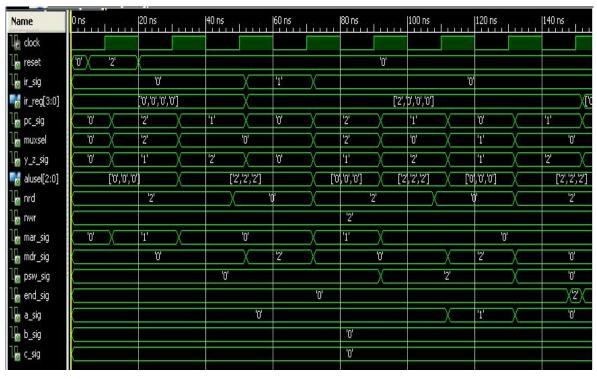

| 4.14a | Simulation results of an instruction (T_MVI A, #nn)                      | 4.30 |

| 4.15  | Simulation results of an instruction (T_STA address)                     | 4.31 |

|       | $\cdot$ – $\prime$                                                       |      |

xiii

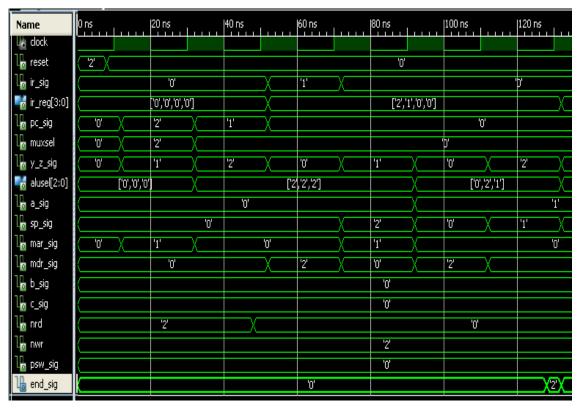

| 4.16 | Simulation results of an instruction (T_JNC offset)               | 4.31 |

|------|-------------------------------------------------------------------|------|

| 4.17 | Simulation results of an instruction (PUSH A)                     | 4.32 |

| 4.18 | Simulation results of an instruction (POP A)                      | 4.32 |

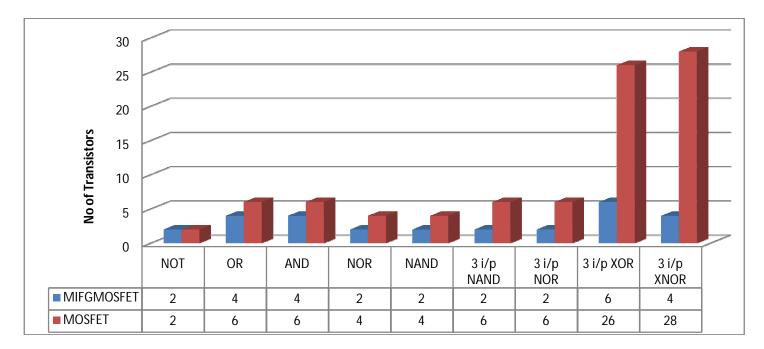

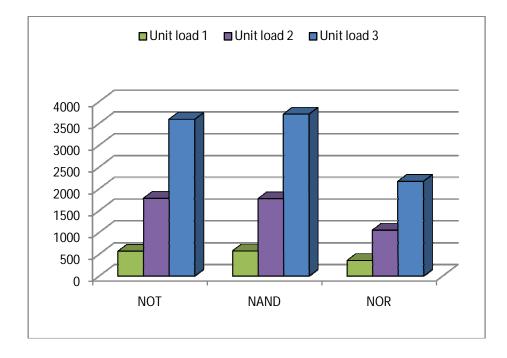

| 5.1  | Comparison of the MIFGMOS and CMOS based approach for             | 5.2  |

|      | the implementations of the binary gates in terms of the           |      |

|      | circuit element count.                                            |      |

| 5.2  | VTC of STI                                                        | 5.3  |

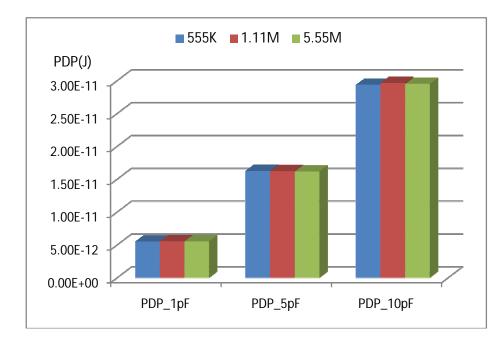

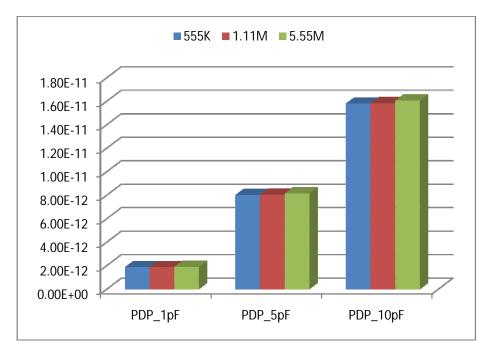

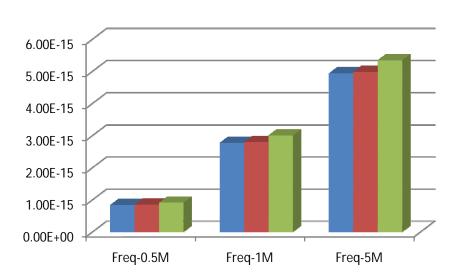

| 5.3  | PDP of ternary gates                                              | 5.6  |

| 5.4  | PDP of TNAND for different capacitive load and frequencies        | 5.6  |

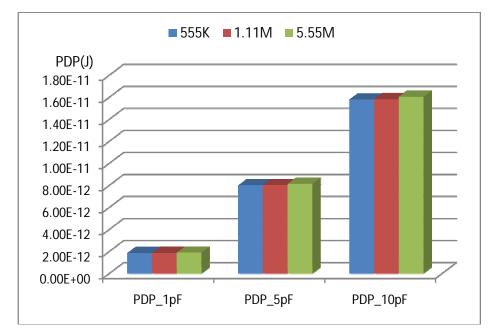

| 5.5  | PDP product of TNOR for different capacitive load and             | 5.6  |

|      | frequencies                                                       |      |

| 5.6  | PDP of TAND for different capacitive load and frequencies         | 5.7  |

| 5.7  | PDP of TAND for different capacitive load and frequencies         | 5.7  |

| 5.8  | Performance analysis of the modified ternary decoder              | 5.8  |

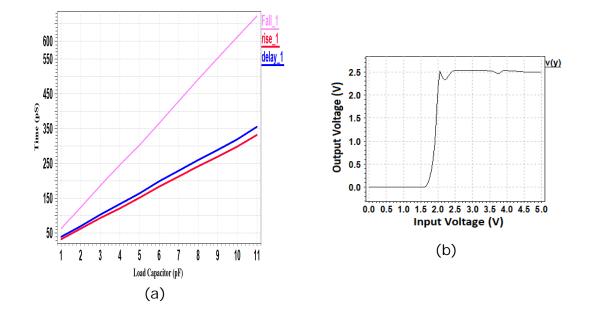

| 5.9  | (a) Performance analysis of the TLS depicting the rise/ fall      | 5.9  |

|      | time and the delay w.r.t the variation in load capacitance.       |      |

|      | (b) VTC curve and the noise margins                               |      |

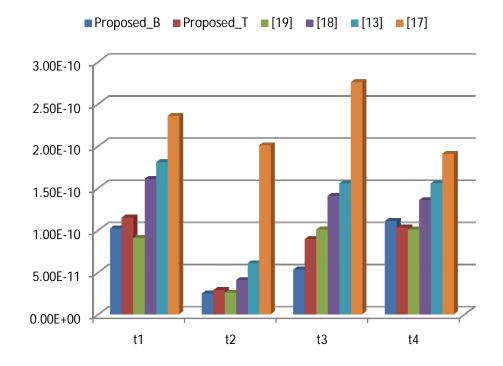

| 5.10 | Transient response of the MIFGMOS THA using both,                 | 5.10 |

|      | ternary logic gates (indicated by $Proposed_T$ ) and binary       |      |

|      | logic gates (indicated by <i>Proposed_B</i> ) compared with other |      |

|      | reported THA                                                      |      |

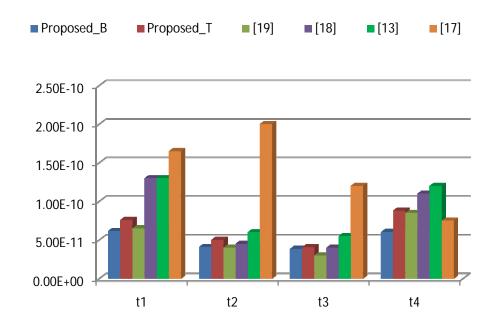

| 5.11 | The transient delay of proposed TM circuit using both,            | 5.10 |

|      | ternary logic gates (indicated by $Proposed_T$ ) and binary       |      |

|      | logic gates (indicated by <i>Proposed_B</i> ) compared with other |      |

|      | reported TM                                                       |      |

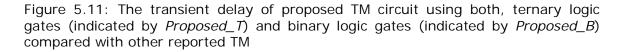

5.12 The RTL schematic of a THA 5.15

## List of Tables

| 2.1  | Summarizes various unary operators for a ternary     | 2.4  |

|------|------------------------------------------------------|------|

|      | logic                                                |      |

| 2.2  | Two place operators like min, max and mod-sum that   | 2.4  |

|      | correspond to the familiar AND, OR, and EXOR         |      |

|      | functions                                            |      |

| 2.3  | Truth table of Standard ternary gates                | 2.7  |

| 2.4  | Truth table of the Ternary gates                     | 2.9  |

| 2.5  | Number of circuit elements used in CNTFET and        | 2.28 |

|      | QDGFET based approaches                              |      |

| 3.1  | Rise time and fall time of ternary gates             | 3.6  |

| 3.2  | Power dissipation across MOS transistor and resistor | 3.6  |

| 3.3  | Truth table of STI, PTI & NTI                        | 3.16 |

| 3.4  | Model simulation parameters and node voltages of the | 3.16 |

|      | designed MIFGMOS transistor based STI circuit        |      |

| 3.5  | Truth table of STNAND                                | 3.19 |

| 3.6  | Truth Table of TNOR Gate                             | 3.22 |

| 3.7  | Truth table of the Ternary gates                     | 3.24 |

| 3.8  | Truth table of the ternary decoder                   | 3.29 |

| 3.9  | Function details of the proposed TALU                | 3.35 |

| 3.10 | Truth table of Ternary Half Adder                    | 3.37 |

| 3.11 | Truth table of Ternary Full Adder                    | 3.39 |

| 3.12 | Truth table of Ternary Multiplier                    | 3.43 |

| 3.13 | Truth table of Ternary Half Subtractor               | 3.44 |

| 3.14 | Truth table of Ternary Full Subtractor               | 3.46 |

| 3.15 | Truth table of Ternary comparator                    | 3.48 |

| 3.16 | Truth table of D flip-flap-flop                      | 3.52 |

| 3.17 | Truth table of Half adder                            | 3.52 |

| 3.18 | Required truth table for counter                     | 3.53 |

| 3.19 | Required truth table for 2 <sup>nd</sup> stage of counter | 3.54 |

|------|-----------------------------------------------------------|------|

| 4.1  | Select line combinations for various arithmetic and       | 4.3  |

|      | logical operations                                        |      |

| 4.2  | The Instruction Set for the design of TCU                 | 4.15 |

| 4.3  | List of various instructions and the assigned codes       | 4.17 |

| 4.4  | Various control signals identified for the TCU            | 4.19 |

| 4.5  | Control sequence for instruction fetch and decode         | 4.22 |

| 4.6  | Control sequence for T_MVI A, #data'                      | 4.22 |

| 4.7  | Control sequence for the execution of instruction         | 4.24 |

|      | 'T_STA addr'                                              |      |

| 4.8  | Control sequence for the execution of instruction 'JNC    | 4.26 |

|      | offset'                                                   |      |

| 4.9  | Control sequence for the execution of instruction         | 4.26 |

|      | 'PUSH A offset'                                           |      |

| 4.10 | Control sequence for the execution of instruction 'POP    | 4.26 |

|      | A'                                                        |      |

| 4.11 | Logical equations for sample control signals              | 4.28 |

| 4.12 | Comparison of the T states in every addressing mode       | 4.33 |

| 5.1  | Noise Margin of STI                                       | 5.3  |

| 5.2  | Rise/ Fall time of the MIFG based STI                     | 5.3  |

| 5.3  | Comparison of number of circuit elements for the          | 5.5  |

|      | implementation of ternary gates                           |      |

| 5.4  | Noise margin of TLS                                       | 5.9  |

| 5.5  | Transient analysis of the designed MIFGMOS transistor     | 5.11 |

|      | for TC and THS                                            |      |

| 5.6  | Comparison of the circuit elements used by the            | 5.12 |

|      | proposed approach with other reported approaches in       |      |

|      | realization of the ternary combinational circuits         |      |

| 5.7  | Logic utilization of the ternary combinational circuits   | 5.14 |

| 5.8  | Timing parameters of the ternary circuits                 | 5.15 |

|      |                                                           |      |

## **ABBREVIATION**

| MVL    | Multi Valued Logic                       |

|--------|------------------------------------------|

| nMOS   | N channel Metal Oxide Semiconductor      |

| pMOS   | p channel Metal Oxide Semiconductor      |

| STI    | Standard Ternary Inverter                |

| PTI    | Positive Ternary Inverter                |

| NTI    | Negative Ternary Inverter                |

| FGMOS  | Field Effect Metal Oxide Semiconductor   |

| PDP    | Power Delay Product                      |

| CMOS   | Complementary Metal Oxide Semiconductor  |

| MIFG   | Multiple Input Field Effect Transistor   |

| HDL    | Hardware Descriptive Language            |

| CNTFET | Carbon Nano Tube Field Effect Transistor |

| QDGFET | Quantum Dot Gate Field Effect Transistor |

| TFA    | Ternary Full Adder                       |

| THA    | Ternary Half Adder                       |

| THS    | Ternary Half Subtractor                  |

| TFS    | Ternary Full Subtractor                  |

| ТМ     | Ternary Multiplier                       |

| ТС     | Ternary Comparator                       |

| TLS    | Ternary Level Shifter                    |

| FIS    | Fuzzy Inference System                   |

| TALU   | Ternary Arithmetic Logic Unit            |

| ANFIS  | Artificial Neuro Fuzzy Inference System  |

# Chapter 1 INTRODUCTION

#### 1.1 Preamble

Traditionally, digital computations are performed on two-valued logic [1]. However, in 1964 *Alexander* has introduced the new technology, Multi Valued Logic (MVL), which can drastically change the concept of the technology [2]. It was expected that the technological advances would bring back the discussion on commercial realization of MVL circuits [3]. The 20<sup>th</sup>century however, brought a focus on ternary radix .The radix *3* number system is known as *Ternary Logic*. As the value of radix increases, the information carrying capacity of each connection also increases.Hence, MVL digital realization would be more appropriate than binary [4]. It offers numerous advantages over the binary logic in the design of the digital system [5]. In MVL many logical and arithmetic operations could be executed with higher speed and smaller number of computation stages [6]. This chapter includes brief Literature survey, Current research status, Motivation, Objectives and Scope of the Research Work and Organization of the Thesis.

#### 1.2 Multi Valued Logic

In 1964, a new technology, MVL, was proposed which can drastically change the concept of the technology. An excellent review of the first developments of MVL and its application to electronics, including a few circuit implementations was presented by *Epstein et al.* [7].MVL has radix greater than 2, while conventional binary logic

computations are performed only on two-valued logic. However, the main drawbacks of the binary integrated circuits are the interconnection and pin-out problems, which result in restrictions, process control and decision support system are not efficiently implementable only with binary logic [8]. To overcome these problems, logic with more than two values, i.e. MVL is used that has the following advantages [1]

- 1. In MVL, each wire can transmit more MVL information than a binary element. As a result, the number of connection inside the chip can be reduced.

- 2. Since each MVL element can process more information than a binary element, the complexity of circuits may be decreased.

- The ON- and OFF-chip connections can be reduced to help alleviate the pin-out difficulties that arise with increasingly larger chips.

- 4. The speed of serial information transmission will be faster since the transmitted information per unit time is increased.

Due to several advantages offered by them over the binary logic, over the past decades, MVL has experienced a phenomenal growth. Unlike the binary logic, in MVL systems there are more than two authorized logic levels. Let us consider an m-valued function F(X) with k variables, where  $X = \{x_1, x_2, x_3, ..., x_k\}$  and each  $x_i$  can adopt values from  $M = \{0, 1, 2, ..., m - 1\}$ . Therefore the function F(X) is a mapping  $f : M^k \rightarrow M$  and consequently there are  $m^{m^k}$  different functions possible in the set f. The logical and arithmetic operations can be performed on more than two logic values. As a result, in MVL many logical and arithmetic operations could be executed with higher speed and smaller number of computation stages [6]. It has therefore been watched with keen interests to overcome the challenges of binary logic

Chapter 1: Introduction

and solve numerous problems more efficiently thus casting its applications in the field of fuzzy logic, machine learning, artificial intelligence, data mining, robotics, digital signal processing, digital control systems and image processing. [4, 6].

Widespread popularity of ternary circuits attracted many contributions from the researchers, taking the baton ahead. P C Balla et al. [9] proposed a MOS ternary-logic family, which is comprised of a set of inverters, NOR gates, and NAND gates. These gates are used to design basic ternary arithmetic and memory circuits. Rozan et al. [10] utilized, VHDL simulator, a hardware description language, as a potential tool for the simulation of MVL logic circuits and systems. The work demonstrates how VHDL can be used as a potential tool for the simulation of multi-valued digital circuits and systems. Masahiro et al. [4] presented a novel ternary fuzzy processor using the logic oriented neural networks. The simulation results are illustrated to show how a ternary fuzzy inference engine can be realized by taking into consideration of advantages of neural networks. Dhande et al. [11, 12] exploited the existing VHDL as a potential EDA tool for the simulation of MVL circuits and system by considering signal 'Z' as one of the state of MVL system along with signals '0' and '1'(0 being ground potential, Z intermediate state and 1 as +5V state). The VHDL modeling and simulation of T-Gates and 1-bit multiplier circuit is described and commented. Sheng et al. [1] designed novel ternary logic gates using Carbon Nano Tube (CNT) FETs (CNTFETs). A resistive-load CNTFETbased ternary logic design has been proposed to implement ternary logic based on CNTFET and compared with the existing resistive-load CNTFET logic gate designs. Supriya et al. [13] discuss logic circuit designs using the circuit model of three-state Quantum Dot Gate Field Effect Transistors (QDGFETs). QDGFETs produce one intermediate

state between the two normal stable ON and OFF states due to a change in the threshold voltage over this range. Chapter 2 details the survey of reported contributions and summarizes their advantages with important findings.

The research contributions focusing on the commercial realization of ternary circuits has grown by leaps and bounds and receives exceptional attention. In spite of the significant advancements, theories predict several disadvantages of MVL and the studies demonstrate challenges in the realization of the ternary circuits.

#### 1.3 Current Status

Following are the major challenges, limitations and unidentified issues which are identified based on the literature survey in the development of ternary logic,

- Only a limited soft computation approaches are explored

- CMOS based approach is popularly used without addressing its major disadvantages

• Use of CNTFET based approach that combines use of ternary and binary gates for design of ternary combinational circuits without detailing the design of Binary CNTFET based gates

• Functionality issue in the design of QDGFET based Ternary full adder.

- Meager attention to design of Ternary Level Shifter (TLS)

- Meager attention to design of ternary sequential circuits

• Simulation tools and VHDL based modeling are not fully exploited to design flexible ternary circuits.

This research addresses some of these challenges and unidentified issues.

#### 1.4 Motivation

The literature reports wide assortment of various methods used for the development of the ternary circuits. The soft computation approaches and simulation tools like VHDL only demonstrate the functionality of the devised circuits without considering the challenges from the realization perspective and may lack sufficiently detailed information of the device.

In the popular CMOS based approaches, the reported disadvantages of high static power, requirement of large off-chip resistors, need of multiple supply voltages, use of depletion-mode MOSFETs outweigh its advantages and make them unsuitable for the upcoming technologies [6]. As reported by *Plummer et al.* [14] the upcoming era will be dominated by beyond CMOS devices. Some of the popular beyond CMOS devices like, the CNTFET are successfully used for the ternary circuits but suffer from large circuit elements and face challenges due to misaligned and mis-positioned CNTs, high resistance CNT metal contact, chemical doping and fabrication issues [6]. The QDGFET based circuits [15] are designed considering 500mV and thus the noise margin is compromised. Moreover, the design TFA needs a careful examination to verify its operation for all the combinations of the input. The meager attention received for the design of TLS is an additional challenge in the development of ternary processor. The use of additional power supplies obviously leads to the power consumption issues related to the voltage divider circuit. Moreover, there are limitations of the voltage divider to act as precise reference. It is

necessary to address this issue and propose a TLS without an additional power supply.

The literature reports wide contributions in VHDL simulation based approaches and device level realizations of various ternary circuits. Despite the potential advantages of ternary logic over the binary, realization of an efficient, realistic and a practical ternary processor is still a thrust area of research. The encouraging results and the limitations in the state of art methods continue to draw attention of the research community and demand further researches to investigate the simulation based approaches and also explore the suitability of other beyond-CMOS devices for the implementation of ternary logic. This research aims to address some of these challenges and unidentified issues in the design of ternary processor.

#### **1.5** Objectives and Scope of the Research Work

This research work is based on ternary logic. The ternary logic is a special case of MVL. The prime objective of this research work is to develop, simulate and test the ternary logic circuits and propose ternary logic processor architecture. This work includes the basic objectives:

1. To carry out an extensive survey of MVL.

2. To study and develop the algebra and calculus of ternary logic.

3. To study various switching devices that supports ternary logic system.

4. To Develop the combinational and sequential ternary logic circuits required to propose the ternary logic processor

5. To propose the basic architecture of ternary logic processor.

6. To simulate and test the basic modules of proposed architecture.

In this research work the modules are simulated using VHDL and performance is evaluated. Hardware implementation of the tested modules is beyond the scope of this research.

#### 1.6 Organization of the Thesis

The thesis is comprised of six chapters. Chapter 1 includes an introduction, the basic terminologies of MVL, its various applications, current status, motivation, objectives and scope of the research work.

Chapter 2 describes the literature survey and review of the existing approaches in designing the ternary circuits. The challenges and the limitations of the existing switching technologies and approaches are highlighted.

Chapter 3 covers the research methodology for exploring the switching device, MIFGMOS in ternary prospects. Novel hybrid approaches for design of ternary combinational and sequential circuits for the ternary processor are presented.

Chapter 4 describes the design and simulation of extended modules for the functional verification of TCU and the ternary instruction set. Chapter 5 presents the results and discussions that detail the contributions of this research.

Chapter 6 comprises of the conclusions and the future scope. The author's research publications are included followed by the references used in this research.

## Chapter 2

## LITERATURE SURVEY

Traditionally, digital computations are performed on two-valued logic named as Binary Logic. The binary logic faces major challenges of the interconnections and pin-out problems when designing large and dense chips. This restricts the number of connections inside and outside of the circuits. However, in 1964, a new technology, MVL, was proposed which can drastically change the concept of the technology.Epstein et al. summarizes the initial developments of MVL and highlights the major applications of MVL across the various domains [16]. MVL systems lead to saving in the number of interconnections. Due to the availability of the additional bits (logic levels), the wires convey more information. It ultimately reduces the number of pins and leads to their saving. The information stored per memory cell also increases with use of MVL. These advantages of MVL directly contribute to reduction in the memory and thus the hardware cost [17]. The significant advantages offered by MVL of reduced complexity in the design, smaller on chip area leading to increased density of fabrication and high-bandwidth parallel and serial data transfer make it an attractive and a thrust area of research [6]. Ternary logic is a specialized MVL that demonstrates use of three significant logic levels, true, false and intermediate.

This chapter presents a Theory of Ternary Logic and survey of the advancements in the ternary domain in terms of the design, realization / implementation and simulation of the ternary gates, combinational and sequential circuits. The chapter also presents a brief survey of the expansion in the MIFG based designs and their usability for ternary logic. The chapter concludes detailing the challenges and issues in the reported literature.

#### 2.1 Ternary Logic

The ternary logic or radix 3 number system, known as *Ternary Logic* is the special case of MVL with three logic levels. Ternary means a switching element, which switches among 3 states namely 0, 1 and 2 voltage states or true, intermediate and false. Many ternary logic models exist in the literature, but they generally involve high power consumption even in static state Customized technological processes [1] or multi-threshold devices [18], Current-mode MVL techniques also exist [9], but they are not feasible for present high performance applications as high-speed performance and low–power dissipation can be obtained using the CMOS technology.

Ternary logic offers several important advantages over the binary logic in the design of the digital system. More information can be transmitted over a given set of lines or stored for a given register length, the complexity of interconnections can be reduced, reduction in the chip area can be achieved and more efficient error detection and error correction code can be employed [9] using Ternary Logic. Additionally the memory requirement will be drastically reduced.

#### 2.1.1 Ternary Logic Preliminaries

Due to the advantages offered by the Ternary Logic the domain is an area of the keen research. The researchers have proposed two different ternary logic systems such as balanced and unbalanced logic system. Balanced or symmetric system uses  $-V_{DD}$  for logic 0, 0V for logic 1 and  $+V_{DD}$  for logic 2. An unbalanced or ordinary system uses OV for logic 0,  $V_{DD}/2$  for logic 1 and,  $V_{DD}$  for logic 2.

In ternary system, i.e. radix 3 system, the numbers of possible functions are  $3^{3^3}$  leading to 19683 logical operations. Max, Min Literals, successor, inverter are few of them which will be detailed in the next section.

#### 2.1.2 Ternary Algebra and Minimization Techniques

Ternary logic demands a functionally complete algebra in order to have the ability to describe all possible functions (19683 logical operations). Since Boolean algebra is not in general adequate for multiple-valued functions due to its lack of completeness over sets of logic values that do not have a cardinality of 2n, it is necessary to consider alternative algebraic structures.

One of the first published ternary logic systems in a modern form was due to the work of Lukasiewicz in Poland in 1920 [19]. This system was motivated by the consideration of a third logic value of *indeterminate* in addition to the values representing *true* and *false*. A variation of the ternary logic system of Lukasiewicz was developed by Bochvar 1939 [20]. The variation was due to a difference in the semantical interpretation of the third logic value. The *indeterminate* logic value as defined by Lukasiewicz was construed by Bochvar as an *undecidable* value. Although the MVL logic of Lukasiewicz was published one year earlier than the work of Emil Post in 1921 [21], the Post algebras are commonly cited as the first example of a MVL algebra since the "chained Post algebra" is functionally complete and that of Lukasiewicz was not. Another ternary logic system was proposed by Kleene in 1938 [22]. As is the case of the Bochvarianternary logic system, the difference in the Kleene system can be considered to be a different interpretation of the third logic value.

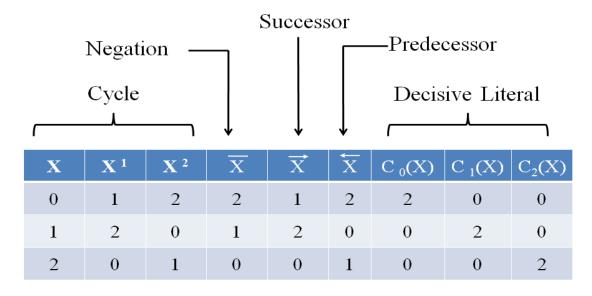

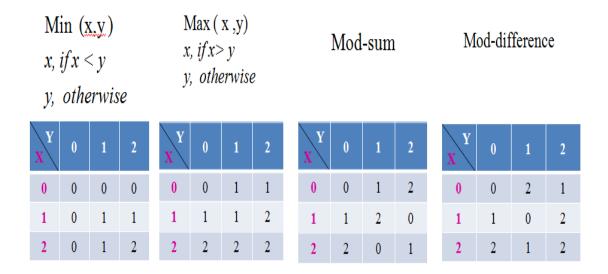

Table 2.1 summarizes various unary operators for ternary logic and table 2.2 shows different operations on unary operators.

Table 2.1: Summarizes various unary operators for a ternary logic

Table 2.2: Two place operators like min, max and mod-sum that correspond to the familiar AND, OR, and EXOR functions

While the system of Lukasiewicz contained the *indeterminate* value and the system of Bochvar an *undecidable* value, the third value in the Kleene system is interpreted as simply an *unknown* value. This interpretation is analogous to the *X* value used in the VHDL and Verilog HDLs for initialization of circuit nets.

The purpose in developing algebra is to provide for a concise well-defined framework for expressing and manipulating functions. In many applications, logic design in particular, a second and equally important consideration is that the operators of the algebra have simple and efficient circuit implementation[20].

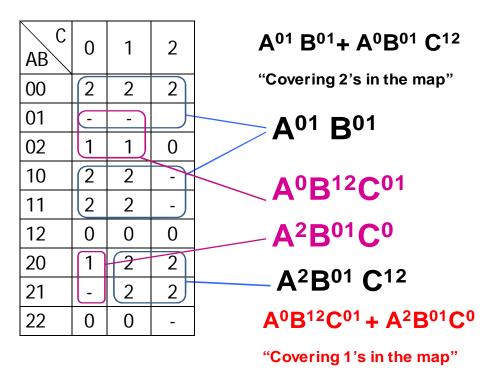

Figure 2.1: Ternary map for 2 and 3 variable

Figure 2.2: Example of ternary map for 3 variable

Binary Karnaugh maps are very effective for functions up to six variables. The key feature of binary K-maps is that only one variable changes when moving from a cell to an adjacent cell. The ternary map in figure 2.1and 2.2 has a similar property and depicts the representation of the 2 and 3 variables. In each square is entered the number of the minterm, which represents it

#### 2.1.3 Ternary Logic Gates

Ternary logic family comprises of set of inverters, NOR gate and NAND gate. These circuits are used to design ternary memory elements and some basic ternary arithmetic circuits like half adder and full adders, and one-ternary multiplier. The circuits thus obtained are then used to synthesize a shift register, an N-bit adder, and an N-bit multiplier. Ternary NOT, NAND and NOR operations seem to be more important

as they are the building blocks of many other complex logical and arithmetic circuits. These fundamental logical functions can be defined in an m-valued k-variable system according to equations detailed below.

#### (i) Inverter

The Yoeli-Rosinfeld algebra [23] defines three basic ternary elements,

- Simple Ternary Inverter (STI)

- Positive Ternary Inverter (PTI)

- Negative Ternary Inverter (NTI)

Logically STI, PTI and NTI are formulated as,

$$STI = \overline{X^{i}} = 2 - X$$

$$PTI, NTI = \overline{X^{i}} = \begin{bmatrix} i \rightarrow X \neq i \\ 2 - i \rightarrow X = i \end{bmatrix}$$

...... 2.1

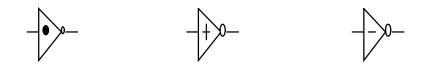

Where, 'i' take the value of '2' for PTI and '0' for NTI inverter. Basic switching elements in the implementation of those inverters are transistors, MOSFETs& RTDs. Figure 2.3 shows the symbols of STI, PTI & NTI. Truth table for the same is given in Table 2.3.

Figure 2.3: Symbols for Inverters (a) STI (b) PTI (c) NTI

Table 2.3: Truth table of Standard ternary gates

| Input | Output |     |     |  |  |

|-------|--------|-----|-----|--|--|

| x     | STI    | PTI | ΝΤΙ |  |  |

| 0     | 2      | 2   | 2   |  |  |

| 1     | 1      | 2   | 0   |  |  |

| 2     | 0      | 0   | 0   |  |  |

#### (ii) TOR and TNOR circuit

Ternary OR is a circuit that has  $X_1 - - X_n$  as input and  $Y_o$  as output such that

$$TOR = X_1 + X_2 + \dots + X_n = Max[X_1, X_2 \dots X_n]$$

..... 2.2

Ternary NOR has an output that is a compliment of OR function i.e.

$$TNOR = \overline{X_1 + X_2 + \dots + X_n} = Max[X_1, X_2 \dots X_n]$$

.....2.3

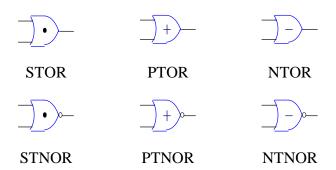

The sign + indicates logical ternary OR operation. Figure 2.4 shows Symbols for TOR/TNOR logic gates

Figure 2.4: Symbols for TOR/TNOR logic gates

Inverter is a basic circuit that is used for implementing TOR/TNOR functions [23]. Depending upon the type of inverter used, the logic functions TOR/TNOR can be

- Simple ternary TOR/TNOR (STOR/STNOR)

- Positive Ternary OR/NOR (PTOR/PTNOR)

- Negative ternary OR/NOR (NTOR/NTNOR)

Table 2.4 shows the truth table of various ternary gates.

#### (iii) TAND and TNAND circuit

Ternary AND , Ternary NAND function is defined as

| TAND  | $= X_{1} \cdot X_{2} \cdot \dots \cdot X_{n} = Min [X_{1}, X_{2}, \dots X_{n}]$            | 2.4 |

|-------|--------------------------------------------------------------------------------------------|-----|

| TNAND | $= \overline{X_1 \cdot X_2 \cdot \dots \cdot X_n} = \overline{Min [X_1, X_2, \dots, X_n]}$ | 2.5 |

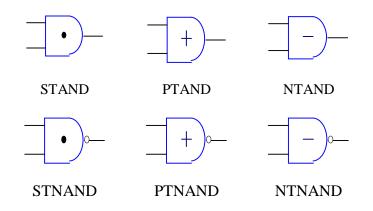

Figure 2.5: Symbols for TAND/ TNAND logic gates

| Α | В | TNAND | TAND | TNOR | TOR | TXOR | TXNOR |

|---|---|-------|------|------|-----|------|-------|

| 0 | 0 | 2     | 0    | 2    | 0   | 0    | 2     |

| 0 | 1 | 2     | 0    | 1    | 1   | 1    | 1     |

| 0 | 2 | 2     | 0    | 0    | 2   | 2    | 0     |

| 1 | 0 | 2     | 0    | 1    | 1   | 1    | 1     |

| 1 | 1 | 1     | 1    | 1    | 1   | 1    | 1     |

| 1 | 2 | 1     | 1    | 0    | 2   | 1    | 1     |

| 2 | 0 | 2     | 0    | 0    | 2   | 2    | 0     |

| 2 | 1 | 1     | 1    | 0    | 2   | 1    | 1     |

| 2 | 2 | 0     | 2    | 0    | 2   | 0    | 2     |

Table 2.4: Truth table of the Ternary gates

Figure 2.5 shows Symbols for TAND/TNAND logic gates.Depending on the type of inverter used, the logic functions TAND/TNAND can be

- Simple ternary TAND/TNAND (STAND/STNAND)

- Positive Ternary AND/NAND (PTAND/PTNAND)

- Negative ternary AND/NAND (NTAND/NTNAND)

#### 2.1.4 Switching Devices For The Realization Of Ternary Logic

Complementary Metal Oxide Semiconductor (CMOS) has been the predominant technology of the past two decades to implement ternary and other MVL systems. Several types of CMOS-based MVL circuits have already been proposed in the literature as the emerging of MOSFET technology. However, they are unsuitable for the current and the upcoming technologies [6]. This encouraged the introduction of some beyond-CMOS nanodevices such as Carbon NanoTube Field Effect Transistor (CNTFET)[6,1], Quantum-dot Cellular Automata (QCA), Single Electron Technology (SET)[6] and Quantum Dot Gate FET (QDGFET) [15] for MVL systems. These nanodevices benefit from low-power consumption, ballistic transport attributes under low supply voltages and very small sizes that make them very suitable for ultralow-power, ultra-high-performance and ultra-high-density chip design [6]. They are considered as a promising choice for future computing technology in many areas including MVL. The present research interests are therefore focused on investigating the utility of such devices for designing ternary systems.

#### 2.2 Multi Input Floating Gate MOSFET (MIFG)

Advancement in VLSI technology has allowed for doubling component density on a silicon chip after every three years. Though MOS transistors have been scaled down, increased interconnections have limited circuit density on a chip. It has become essential to explore other methods of adding more functionality to a MOS transistor. Multiple Input Floating Gate (MIFG) MOS transistor is one such switching device which has made it possible to implement ternary circuits using fewer transistors and reduced interconnections. A novel approach based on utilization of MIFG MOS transistor for the realization of the ternary circuits is a major contribution of this research. The theoretical foundations of MIFG are detailed in this section.

### 2.2.1 MIFG As A Switching Device For Realization Of Ternary Circuits

MIFG is a functional MOS transistor that works more intelligently than a mere switching device. The functional transistor calculates weighted sum of all input signals at the gate level, and controls the "ON" and "OFF" state of the transistor based on the result of such a weighted sum operation. The proposed research aims to explore the usefulness of MIFGMOS transistor for the design and simulation of ternary logic circuits.

The floating gate voltage is proportional to the stored charge and the charge is proportional to the input voltages capacitively coupled. Upon modifying the charge, the floating gate voltage will change. So, the current through the transistor also will change according to the input voltages. This makes it possible to achieve the desired third state as defined in case of a ternary logic. The device thus outperforms when explored from the ternary perspective. It is similar to MOSFET in terms of inherent electronic characteristics. On account of this similarity, previously designed structures based on CMOS platforms can still be utilized in MIFGMOS transistor based design. MIFG, as explored in this research proves to be an efficient switching device for the realization of the ternary circuits. Figure 2.6 depicts the symbol of MIFG.

Figure 2.6: MIFG MOSFET Symbol

### 2.2.2 Structure Of MIFG

The structure of MIFG MOSFET, as shown in Figure 2.7 comprises of the floating gate and number of input gates built on poly2, which is coupled to poly1 gate by capacitors between poly1 and poly2. This structure makes it possible for multi- input floating gate devices to be implemented in double polysilicon CMOS process. The floating gate in the MOSFET extends over the channel and the field oxide. A number of control gates, which are inputs to the transistor, are formed over the floating gate using a second polysilicon layer (poly 2) [24].

Figure 2.7: Possible Layout Of a 3-input n-channel FGMOS transistor(middle) and its cross-sectional views (A, B and C)[25]

The device is composed of a floating gate and multiples of input gates that are capacitively interacting with the floating gate. As the gate-level sum operation is performed in a voltage mode utilizing the capacitive coupling effect, essentially no power dissipation occurs in the calculation, making the device ideal for ULSI implementation.

Figure 2.8: Simplified structure of MIFGMOS transistor

Figure 2.8 depicts a simplified structure of MIFGMOS transistor [26]. They have the same basic properties as equivalent to ordinary MOS transistors but widened by certain additional features. The most significant of them, there is the ability of summing gate controlling input signals as well as the possibility of reduction of threshold value voltage [26]. Let V<sub>th</sub> be the threshold voltage of the transistor. The transistor turns on at the condition where the potential at the floating gate exceeds the threshold voltage, i.e.  $\phi_F > V_{th}$ , and is described by the eq. 2.6 and 2.7 [26]

$$\emptyset_F(t) = \emptyset_F(0) + \frac{\sum_{i=1}^n (C_i V_i(t) - C_i V_i(0))}{\sum_{i=0}^n C_i} \qquad \dots \dots 2.6$$

Where,

n is the number of inputs

$\phi_{F}(t)$  is the potential at the floating gate

V<sub>th</sub> is the threshold voltage

$$\frac{V_1 C_1 + V_2 C_2 \dots V_n C_n}{C_1 + C_2 \dots C_n + C_0} > V_{th}$$

...... 2.7

Synthesis and Simulation of Novel MVL Processor Architecture 2.14

These transistors can operate as normal MOS as saturated or non-saturated within the region of strong inversion or typically within the region of weak inversion called sub-threshold region. That second operating region is utilized in electronic circuits with very low supply voltage [27].

Figure 2.8(a) shows capacitive coupling between the multipleinput gates and floating gate and the channel. Figure 2.8(b)  $C_1$ ,  $C_2$ ,  $C_3$ and  $C_n$  are the coupling capacitors between the floating gate and the inputs. The corresponding terminal voltages are V<sub>1</sub>, V2, V3,...,Vn, respectively.  $C_0$  is the capacitor between the floating gate and substrate. VSS is the substrate voltage.  $Q_1$ ,  $Q_2$ ,  $Q_3$ , ...,Qn are the charges stored in corresponding capacitors  $C_1$ ,  $C_2$ ,  $C_3$ , ..., Cn.

The multi-input floating gate MOSFET operation depends on the weighted sum of voltages at input nodes, which are capacitively coupled to the gate.

### 2.2.3 IV Characteristics of MIFG

Figure 2.9 shows the output IV characteristics of n channel and p channel MIFGMOS transistor operated under identical voltage levels i.e. 3V, which confirm the design considerations of the proposed approach. Eq. 2.8, 2.9 and 2.10 represent the modeling equations of the MIFGMOS transistor [26].

As clear from the characteristics and the modelling equation, the three operating region of MIFGMOS transistor are cut off, strong inversion ohmic and strong inversion saturation. In cut-off region, gate to source voltage,  $V_{gs}$  is less than the threshold voltage  $V_{th}$  and no current flows through the device making it act like a open switch. Whereas in strong inversion ohmic region,  $V_{gs}$  is greater the  $V_{th}$  and the device behaves like a resistor. In strong inversion saturation region, the device is fully ON and behaves as closed switch.

Figure 2.9: IV characteristics of (a) nMIFGMOS transistor (b) pMIFGMOS transistor

Cut off region

$I_D = 0$

$V_{GS} < V_T \dots 2.8$

Strong Inversion Ohmic region

$$I_{D} = \frac{\beta}{2} \left\{ \left[ \left( \sum_{i=1}^{N} \frac{C_{i}}{C_{T}} V_{iS} - \left( V_{T} - \frac{C_{GB}}{C_{T}} V_{BS} - \frac{Q_{FG}}{C_{T}} \right) \right) \right] - \left( \frac{1}{2} - \frac{C_{GD}}{C_{T}} \right) V_{DS} \right\}$$

For

$$0 < V_{DS} \leq \left( \sum_{i=1}^{N} \frac{C_{i}}{C_{T}} V_{iS} + \frac{C_{GD}}{C_{T}} V_{DS} + \frac{C_{GB}}{C_{T}} V_{BS} + \frac{Q_{FG}}{C_{T}} - V_{T} \right)$$

$$V_{GS} > V_{T} \qquad \dots 2.9$$

Strong Inversion Saturation region

$$I_{D} = \frac{\beta}{2} \left( \sum_{i=1}^{N} \frac{C_{i}}{C_{T}} V_{iS} + \frac{C_{GD}}{C_{T}} V_{DS} + \frac{C_{GB}}{C_{T}} V_{BS} + \frac{Q_{FG}}{C_{T}} - V_{T} \right)^{2}$$

For ...2.10

$$0 < \left( \sum_{i=1}^{N} \frac{C_{i}}{C_{T}} V_{iS} + \frac{C_{GD}}{C_{T}} V_{DS} + \frac{C_{GB}}{C_{T}} V_{BS} + \frac{Q_{FG}}{C_{T}} - V_{T} \right) \le V_{DS}$$

$$V_{GS} > V_{T}$$

Several effects can be observed from these equations:

• The floating-gate transistor can go into depletion-mode

operation and can conduct current even when |VGS| < |VT|. This is because the channel can be turned on by the drain voltage through the *f VDs*.

Region 2 for the conventional MOS transistor is the saturation region where *I<sub>DS</sub>* is essentially independent of the drainvoltage. This is no longer true for the floating-gate transistorin which the drain current will continue to rise as the drainvoltage increases and saturation will not occur.

The floating gate voltage is proportional to the stored charge and this is further proportional to the input voltages capacitively coupled. Upon modifying the charge, the floating gate voltage will change. So, the current through the transistor also will change according to the input voltages thus making it possible to achieve the desired states in the ternary logic.

### 2.2.4 Concept of Variable Switching Voltage in MIFG

The conductivity of the floating-gate MOS transistor differs from that of a conventional MOS transistor having the same applied terminal voltages due to a capacitive coupling between the drain region and the floating gate. When a voltage is applied to the drain region, capacitive coupling between the drain and the floating gate induces a high electrical potential on the floating gate. This induced field on the floating gate then modifies the conductivity of the underlying channel region. The uniqueness of multi-input floating gate MOSFET lies in the fact that the switching voltage can be varied by selection of those capacitor values through which the inputs are coupled to the gate. In conventional MOSFET, varying the W/L ratios of the MOSFET varies the threshold voltage. In multi- input floating gate MOSFET, varying the coupling capacitances to the gate can vary the switching point in DC transfer characteristics.

By providing various fixed input voltages at different gates, the floating gate voltage,  $\Phi_F$  can be varied thereby adjusting the charge on the floating gate. The input voltage at the floating gate is the weighted sum of all the individual input voltages, with the capacitances acting as the weights. So, by fixing the input voltage at a gate to either V<sub>DD</sub> or GND, the average input voltage can be varied effectively varying the threshold voltage level of the PMOS and NMOS MIFG transistor pair. Hence, the output switches its state at different input voltages just as it would if the W<sub>p</sub>/W<sub>n</sub> ratio were to be varied.

This ability to alter the charge during operation on a floating gate transistor allows its effective utilization in realization of the multi valued logic circuits.

#### 2.3 Review of Digital Ternary Logic Systems

With the development of MVL by **Post** and **Lukasiewicz** in 1920, several attempts have been made to use this concept in computer science [16]. Since **R.E. Miller(1965)** proposed in his book on "switching theory, John wiley, 1965" that base three system is most efficient number system, the concept of the ternary based computations and the required algebra was developed. **Yoeli et al.** [28] developed the algebra for logical design of ternary switching circuits and attracted the interests of many researchers [29]. An excellent review of the first developments of MVL and its application to electronics, including a few circuit implementations was presented by **Epstein et al.(1974)** [7] considering the area of MVL was an emerging thrust area with special focus on ternary logic. Ternary functions were studied in detail from the standpoint of their functional

completeness or representations.

*Mukaidono et al. (1981)* introduced some special subsets of ternary functions called regular, normal and uniform. When applying the ternary functions to various fields of engineering, it is seldom that all the functions are used. So only some subsets of ternary logic were identified in their research with special properties and meaning. These ternary functions are popularly used in various field of engineering like switching theory, programming languages, algorithm theory and many other fields [30]. Ternary logic was thus continued to be explored to replace binary logic and other applications.

**Bala et al. (1984)** proposed a MOS ternary-logic family, which is comprised of a set of inverters, NOR gates, and NAND gates. These gates are used to design basic ternary arithmetic and memory circuits. The circuits thus obtained are then used to synthesize complex ternary arithmetic circuits and shift registers. The ternary circuits developed are shown to have some significant advantages relative to other known ternary circuits like low power dissipation, and reduced propagation delay and component count. For a given dynamic range, the complexity of the new ternary circuits is shown to be comparable to that of corresponding binary circuits. Nevertheless, the associated reduction in the word-length in the case of the ternary circuits tends to alleviate to a large extent the pin limitation problem associated with VLSI implementation. The cyclic convolution, an application is implemented in which a significant advantage can be gained through the use of ternary digital hardware [9].

With the recent technological advancements, commercial realization of ternary circuits is watched with keen interest. Literature

reports various simulation tools like SPICE and VHDL simulator to design various building blocks and fundamental elements of a ternary processor.

*Mouetal.* (1986) proposed a new scheme in which ternary clocking signals are used to replace the binary clocking signals in VLSI scan testing designs. The clocking scheme exploits the ternary logic to eliminate the mode selecting line and reduce the interconnection problem and the chip area and has the same advantage of high testability as the binary scan method. [31]

**Seger et al. (1988)** presented one such application of ternary logic in developing a model for detection of timing problems in digital networks. The ternary logic based model is closely related to the binary almost-equal-delay-model and is considerably more efficient. It could also be easily incorporated in the simulators [32]. The novel ternary algorithm is capable of detecting critical races under the assumption that all delays are approximately but not exactly equal. A major disadvantage with the ternary algorithm is that it is not guaranteed to halt, leading to an argument that a practical circuit that does not stabilize in say, ten races is not very well designed.

*Wang et al. (1988)* developed a new dynamic ternary logic and its circuit structures to achieve the goal of low power dissipation and high operation. The devised approach implements YoeliRosenfield algebra however, needs four phase clocking scheme. The dynamic CMOS ternary logic has advantages of low power, small area and high speed. Moreover, it can be implemented by the CMOS process used by the binary circuits[29]. In another research by *Morisue et al.*

(1989) Josephson junction and its tri-stable-state has been utilized to construct several circuits in ternary form [33, 34].

**Rizvi et al. (1991)**on the other hand designed a spatial filtering Location Addressable Memory [LAM] in ternary logic that is capable of handling multi-input multi-output in an efficient way. The LAM device can be used in the truth table lookup implementation processor in ternary logic. The devised approach is validated by implementing ternary combinational circuits like ternary half adder and ternary Subtractor [35].

**Rozan et al. (1996)** utilized, VHDL simulator, a hardware description language, as a potential tool for the simulation of MVL logic circuits and systems. The work demonstrates how VHDL can be used as a potential tool for the simulation of multi-valued digital circuits and systems. Although not all features of a given VHDL simulator can be applied to MVL signals, some can easily be adapted to provide enough information to verify functionality and/or timing specifications. The VHDL modeling and simulation of two simple ternary circuits are described and commented [10].

Jones et al. (1996) focused his research on ternary algebra and modeling to discuss the simultaneous existence and relationships, between binary and ternary. Their research defined the various interpretations and rules that can be applied to the simultaneous existence. Finally the formulated rules were utilized the further implicit dynamics of ternary relationships when multiple binary relationships are imposed [36]. **Masahiro et al. (1997)** presented a novel ternary fuzzy processor using the logic oriented neural networks. The simulation results are illustrated to show how a ternary fuzzy inference engine can be realized by taking into consideration of advantages of neural networks. The principle to construct a ternary processor using the neural networks is described in detail and the simulation results for a novel Max circuit which is the essential circuit of the fuzzy inference engine are given. The features of the proposed processor are capability of high speed operation, and very simple construction with less number of elements to perform a function of fuzzy processor [4].

**Serran et al. (1997)** presented a proposal for the implementation of ternary digital circuits. Their study described a new multivalued algebra that uses the Post's cyclic negation, the AND conjunction and new operators which allow the development of simple algorithms for the synthesis and simplification of the logical function. An electronic implementation of a ternary logic is also presented in their investigation [37].

*Srivastava et al. (2000)* on the other hand implemented the ternary functions mainly by adjusting the W/L ratios of the transistors in a CMOS inverter and by using a transmission gate at the output. Back-gate bias provides an additional parameter in the design of CMOS ternary logic circuit for the low voltage operation to generate the desired DC voltage transfer characteristics and transition region adjustment. Key building blocks – a STI, PTI and NTI are designed using the proposed method [38].

**Nascimento et al. (2001)** attempted to design a perfect automated tool for analysis and design of MVL digital circuits. They presented software called *ELOmv*, is capable of calculating the truth table for expressions in ternary or quaternary level with even three variables of entry. This software is a tool that can be used in a future work in which synthesis and simplification of logical functions will be performed [39].

**Yamamoto et al. (2003)** defined an extension of the ternary majority function using cyclic operation to I/O values of the function. The extended ternary majority functions are functionally complete on a ternary logic system and enable the representation of any ternary logic. Genetic Algorithm (GA) is used as a tool and an advanced method applicable to many variable case is proposed together with some experiments [40].

*Maddess et al. (2004)* explored the utility of ternary logic for texture representation. A systematic method for producing texture pattern is recognized for creating a large number of classes of binary (256) and ternary (7.62 x  $10^{12}$ ) textures. Their study presents guidelines and analytical methods for selecting sets of textures with particular image qualities and non-linear relationships between pixels. Given the large number of patterns, there are undoubtedly many applications other than image processing and pattern recognition that demand the wide patterns for representing the two or three brightness levels or colors[41].

**Raychowdhury et al. (2004)** 2004 presented a novel method of multiple-valued logic design using CNTFETs. The geometry dependant

threshold voltage of these transistors has been used to design a ternary logic family HSPICE has been used in all simulations and transient as well as dc characteristics have been studied [18].

*Gundersen et al. (2005)* explored the switching devices for the realization of ternary circuits. A novel voltage non-inverting CMOS Semi-Floating- Gate (SFG) ternary switching element is presented. This element shows good noise margin and is easy to fine tune, and it is well suitable to use in refreshing ternary signals in memory applications. [42].